# DisplayPort<sup>TM</sup> Standard

860 Hillview Court, Suite 150 Milpitas, CA 95035

Phone: 408 957 9270 Fax: 408 957 9277 URL: www.vesa.org

# **VESA DisplayPort Standard**

Version 1, Revision 1a January 11, 2008

## **Purpose**

The purpose of this document is to define a flexible system and apparatus capable of transporting video, audio and other data between a Source Device and a Sink Device over a digital communications interface.

## **Summary**

The DisplayPort<sup>TM</sup> standard specifies an open digital communications interface for use in both internal connections, such as interfaces within a PC or monitor, and external display connections, including interfaces between a PC and monitor or projector, between a PC and TV, or between a device such as a DVD player and TV display.

DisplayPort.1.1a is revised to correct errata items in, and add clarifications to, DisplayPort Standard 1.1.

# **Table of Contents**

| Acknowledgements                                                                            | 11 |

|---------------------------------------------------------------------------------------------|----|

| Revision History                                                                            | 14 |

| I Introduction                                                                              | 17 |

| 1.1 DisplayPort Specification Organization                                                  | 17 |

| 1.2 DisplayPort Objectives                                                                  |    |

| 1.2.1 Key Industry Needs for DisplayPort                                                    |    |

| 1.2.2 DisplayPort Technical Objectives                                                      |    |

| 1.2.3 DisplayPort External Connection Objectives                                            |    |

| 1.2.4 DisplayPort Internal Connection Objectives                                            |    |

| 1.2.5 DisplayPort CE Connection Objectives                                                  | 20 |

| 1.2.6 Content Protection for DisplayPort                                                    |    |

| 1.3 Acronyms                                                                                |    |

| 1.4 Glossary                                                                                | 22 |

| 1.5 References                                                                              | 26 |

| 1.6 Nomenclature for Bit and Byte Ordering                                                  |    |

| 1.6.1 Bit Ordering                                                                          | 27 |

| 1.6.2 Byte Ordering                                                                         |    |

| 1.7 Overview of DisplayPort                                                                 | 29 |

| 1.7.1 Make-up of the Main Link                                                              | 29 |

| 1.7.2 Make-up of AUX CH                                                                     | 30 |

| 1.7.3 Link Configuration and Management                                                     | 31 |

| 1.7.4 Layered, Modular Architecture                                                         | 31 |

| 2 Link Layer                                                                                | 33 |

| 2.1 Introduction                                                                            | 33 |

| 2.1.1 Number of Lanes and Per-lane Data Rate                                                |    |

| 2.1.2 Number of Main, Uncompressed Video Streams                                            |    |

| 2.1.3 Basic Functions                                                                       |    |

| 2.1.4 DisplayPort Device Types and Link Topology                                            |    |

| 2.2 Isochronous Transport Services                                                          |    |

| 2.2.1 Main Stream to Main Link Lane Mapping in the Source Device                            |    |

| 2.2.2 Stream Reconstruction in the Sink                                                     |    |

| 2.2.3 Stream Clock Recovery                                                                 |    |

| 2.2.4 Main Stream Attribute Data Transport                                                  |    |

| 2.2.5 Secondary-data Packing Formats                                                        |    |

| 2.2.6 ECC for Secondary-data Packet                                                         |    |

| 2.3 AUX CH States and Arbitration.                                                          |    |

| 2.3.1 AUX CH STATES Overview                                                                |    |

| 2.3.2 Link Layer Arbitration Control                                                        |    |

| 2.3.3 Policy Maker AUX CH Management                                                        |    |

| 2.3.4 Detailed Source AUX CH State Description                                              |    |

| 2.3.5 Detailed Sink AUX CH State Description                                                |    |

| 2.4 AUX CH Syntax                                                                           |    |

| 2.4.1 Command definition                                                                    |    |

| 2.4.2 AUX CH Response / Reply Time-outs                                                     |    |

| 2.4.3 Native AUX CH Request Transaction Syntax                                              |    |

| 2.4.4 Native AUX CH Reply Transaction Syntax                                                |    |

| 2.4.5 I <sup>2</sup> C bus transaction mapping onto AUX CH Syntax                           |    |

| 2.4.6 Conversion of I <sup>2</sup> C Transaction to Native AUX CH Transaction (INFORMATIVE) |    |

|   |                      | X CH Services                                          |            |

|---|----------------------|--------------------------------------------------------|------------|

|   | 2.5.1                | Stream Transport Initiation Sequence                   |            |

|   | 2.5.2                | Stream Transport Termination Sequence                  | 118        |

|   | 2.5.3                | AUX CH Link Services                                   | 119        |

|   | 2.5.4                | AUX CH Device Services                                 | 141        |

| 3 | Physica <sup>1</sup> | l Layer                                                | 143        |

|   | 2.1 14.              |                                                        | 1.42       |

|   |                      | oduction                                               |            |

|   | 3.1.1                | PHY Functions                                          |            |

|   | 3.1.2                | Link Layer-PHY Interface Signals                       |            |

|   | 3.1.3                | PHY-Media Interface Signals                            |            |

|   | -                    | _PWR for Box-to-Box DisplayPort Connection             |            |

|   | 3.2.1                | DP_PWR User Detection Method                           |            |

|   | 3.2.2                | DP_PWR Wire                                            |            |

|   | 3.2.3                | Inrush Current                                         |            |

|   | 3.2.4                | Voltage Droop                                          |            |

|   | 3.2.5                | Over Current Protection (OCP)                          | 147        |

|   | 3.3 Hot              | t Plug/Unplug Detect Circuitry                         | 148        |

|   | 3.4 AU               | X Channel                                              | 148        |

|   | 3.4.1                | AUX Channel Logical Sub-Block                          | 149        |

|   | 3.4.2                | AUX Channel Electrical Sub-Block                       | 151        |

|   | 3.5 Ma               | in Link                                                | 155        |

|   | 3.5.1                | Main Link Logic Sub-block                              |            |

|   | 3.5.2                | Main Link Electrical Sub-Block                         |            |

|   | 3.5.3                | Transmitter and Receiver Electrical Specifications     |            |

|   | 3.5.4                | ESD and EOS Protection                                 |            |

| 1 |                      | ical                                                   |            |

| • |                      |                                                        |            |

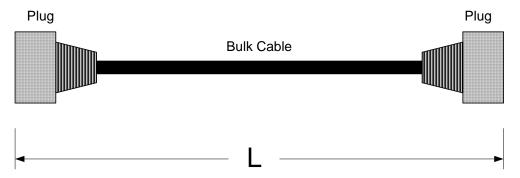

|   | 4.1 Cab              | ble-Connector Assembly Specifications (for box-to-box) |            |

|   | 4.1.1                | Cable-Connector Assembly Definition                    | 182        |

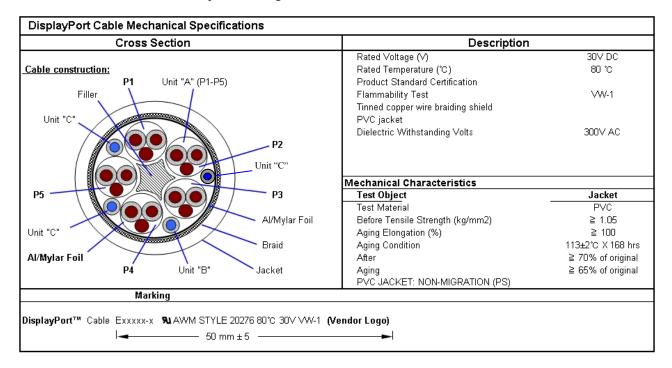

|   | 4.1.2                | Type of Bulk Cable                                     |            |

|   | 4.1.3                | Impedance Profile                                      | 184        |

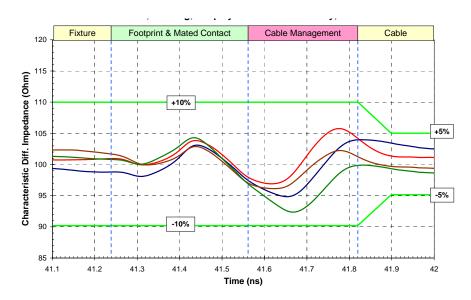

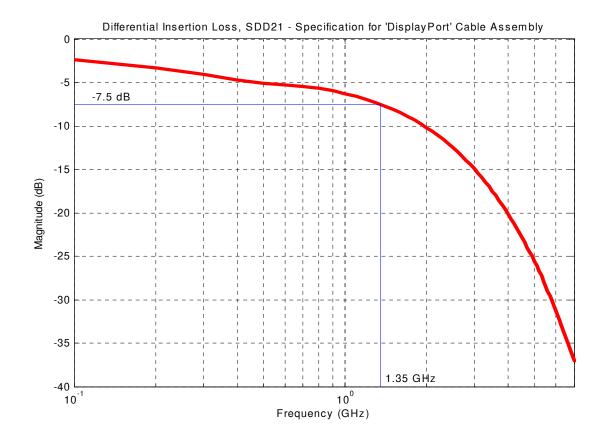

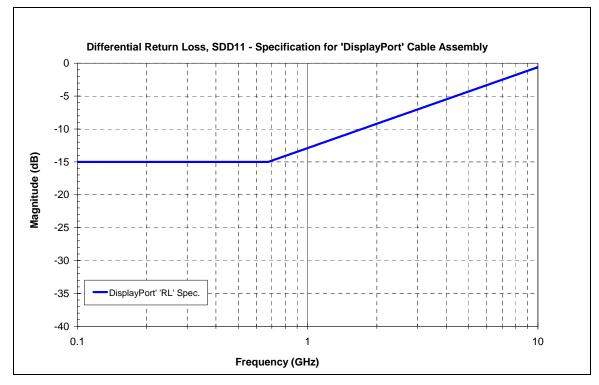

|   | 4.1.4                | Insertion Loss & Return Loss                           | 184        |

|   | 4.1.5                | High-bit-rate Cable-Connector Assembly Specification   | 185        |

|   | 4.1.6                | Reuced Bit Rate Cable-Connector Assembly Specification |            |

|   | 4.2 Cor              | nnector Specification                                  |            |

|   | 4.2.1                | External connector                                     |            |

|   | 4.2.2                | Panel-side Internal Connector (Informative)            |            |

| 5 |                      | Sink Device Interoperability                           |            |

|   |                      | • •                                                    |            |

|   | 5.1 Sou              | rce Device                                             |            |

|   | 5.1.1                | Stream Source Requirement                              |            |

|   | 5.1.2                | Source Device Link Configuration Requirement           | 218        |

|   | 5.1.3                | Source Device Behavior on Stream Timing Change         | 218        |

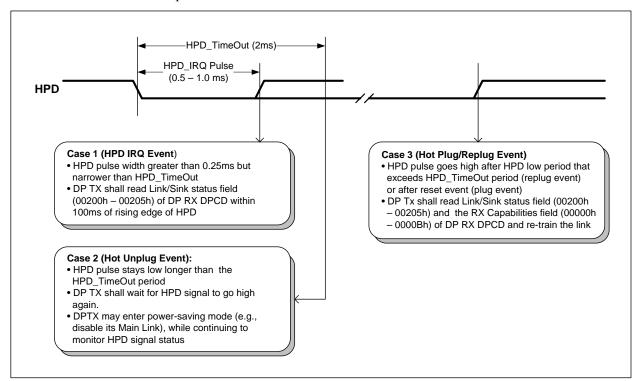

|   | 5.1.4                | Source Device Behavior upon HPD Pulse Detection        | 219        |

|   | 5.1.5                | Sink Device Power Management by a Source Device        | 220        |

|   | 5.2 Sin              | k Device                                               |            |

|   | 5.2.1                | Stream Sink Requirement                                |            |

|   | 5.2.2                | Sink Device Link Configuration Requirement             |            |

|   | 5.2.3                | Sink Device Behavior on Stream Timing Change           |            |

|   | 5.2.4                | Toggling of HPD Signal for Status Change Notification  |            |

|   | 5.2.5                | Sink Device Power-Save Mode                            |            |

|   |                      | nch Device                                             | 223<br>273 |

| 5.3.1 EDID Access Handling Requirement                                                                       | 223 |

|--------------------------------------------------------------------------------------------------------------|-----|

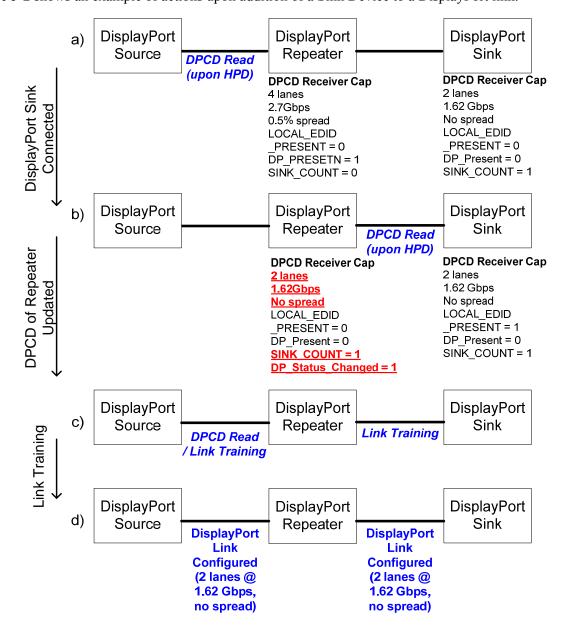

| 5.3.2 Branch Device Link Configuration Requirements                                                          |     |

| 5.4 Cable-Connector Assembly                                                                                 |     |

| 5.4.1 Box-to-Box, End-User-Detachable Cable Assembly                                                         | 227 |

| 5.4.2 Embedded and Captive Cable Assembly                                                                    | 227 |

| 6 Appendix A: Link Layer Extension for DPCP Support                                                          | 228 |

| 6.1 DPCP Bulk Encryption/Decryption Blocks                                                                   | 228 |

| 6.2 AUX CH Transactions for DPCP.                                                                            |     |

| 7 Appendix B: Audio Transport ( <i>Informative</i> )                                                         |     |

| * * * * * * * * * * * * * * * * * * * *                                                                      |     |

| <ul> <li>7.1 Audio stream components</li> <li>7.2 Association of Three Packet Types via Packet ID</li> </ul> | 229 |

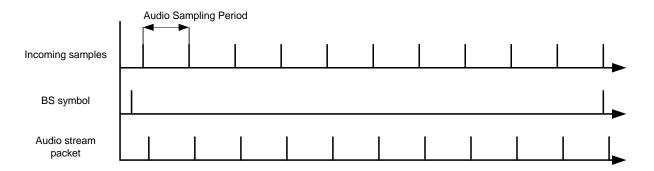

| 7.3 Scheduling of Audio Stream Packet Transmission                                                           |     |

| 7.3.1 Handling of an Audio Format Change                                                                     |     |

| 7.4 Structure of Audio Stream Packet                                                                         |     |

| 7.4.1 One or Two Channel Audio                                                                               |     |

| 7.4.2 Three to Eight Channel Audio                                                                           |     |

| 7.5 Channel-to-Speaker Mapping                                                                               |     |

| 7.6 Transfer of Sample Frequency Information                                                                 | 233 |

| 8 Appendix C: Sink Event Notification Example (Informative)                                                  | 234 |

| 8.1 Mutual Identification by Source and Sink                                                                 | 234 |

| 8.2 IRQ HPD Pulse and Sink-Specific IRQ                                                                      |     |

| 9 Appendix D: Summary of Features Related to Power Management (Informative)                                  |     |

| 9.1 AUX CH Request Transaction Readiness by Sink Device                                                      |     |

| 9.2 Source Detection                                                                                         |     |

| 9.3 Link Training without AUX CH Handshake (Fast Link Training)                                              |     |

| 10 Main Contributor History (Previous Versions)                                                              |     |

| Table 0-1: Main Contributors to Version 1.1a                                                                 | 11  |

| Table 1-1: List of Acronyms                                                                                  |     |

| Table 1-2: Glossary of Terms                                                                                 |     |

| Table 1-3: Reference Documents                                                                               | 26  |

| Table 2-1: Control Symbols for Framing.                                                                      |     |

| Table 2-2: Pixel Steering into Main Link Lanes                                                               |     |

| Table 2-3: VB-ID Bit Definition                                                                              |     |

| Table 2-4: 30 bpp RGB (10 Bits/Component) 1366 x 768 Packing to a Four Lane Main Link                        |     |

| Table 2-5: 24 bpp RGB to a Four Lane Main Link Mapping                                                       |     |

| Table 2-6: 24 bpp RGB Mapping to a Two Lane Main Link                                                        |     |

| Table 2-8: 18 bpp RGB Mapping to a Four Lane Main Link                                                       |     |

| Table 2-9: 18 bpp RGB Mapping to a Two Lane Main Link                                                        |     |

| Table 2-10: 18 bpp RGB Mapping to a One Lane Main Link                                                       |     |

| Table 2-11: 30 bpp RGB Mapping to a Four Lane Main Link                                                      |     |

| Table 2-12: 30 bpp RGB Mapping to a Two Lane Main Link                                                       |     |

| Table 2-13: 30 bpp RGB Mapping to a One Lane Main Link                                                       | 51  |

| Table 2-14: 36 bpp RGB Mapping to a Four lane Main Link                                                      |     |

| Table 2-15: 36 bpp RGB Mapping to a Two Lane Main Link                                                       |     |

| Table 2-16: 36 bpp RGB Mapping to a One Lane Main Link                                                       |     |

| Table 2-17: 48 bpp RGB Mapping to a Four Lane Main Link                                                      | 53  |

|                                                                                                              |     |

| Table 2-18: 48 bpp RGB Mapping to a Two Lane Main Link                                                      | 53  |

|-------------------------------------------------------------------------------------------------------------|-----|

| Table 2-19: 48 bpp RGB Mapping to a One Lane Main Link                                                      |     |

| Table 2-20: 16 bpp YCbCr 4:2:2 Mapping to a Four Lane Main Link                                             |     |

| Table 2-21: 16 bpp YCbCr 4:2:2 Mapping to a Two Lane Main Link                                              |     |

| Table 2-22: 16 bpp YCbCr 4:2:2 Mapping to a One Lane Main Link                                              |     |

| Table 2-23: 20 bpp YCbCr 4:2:2 Mapping to a Four Lane Main Link                                             |     |

| Table 2-24: 20 bpp YCbCr 4:2:2 Mapping to a Two Lane Main Link                                              |     |

| Table 2-25: 20 bpp YCbCr 4:2:2 Mapping to a One Lane Main Link                                              |     |

| Table 2-26: 24 bpp YCbCr 4:2:2 Mapping to a Four Lane Main Link                                             |     |

| Table 2-27: 24 bpp YCbCr 4:2:2 Mapping to a Two Lane Main Link                                              |     |

| Table 2-28: 24 bpp YCbCr 4:2:2 Mapping to a One Lane Main Link                                              |     |

| Table 2-29: 32 bpp YCbCr 4:2:2 Mapping to a Four Lane Main Link                                             |     |

| Table 2-30: 32 bpp YCbCr 4:2:2 Mapping to a Two Lane Main Link                                              |     |

| Table 2-31: 32 bpp YCbCr 4:2:2 Mapping to a One Lane Main Link                                              |     |

| Table 2-32: Transfer Unit of 30 bpp RGB Video Over a 2.7 Gbps Per Lane Main Link                            |     |

| Table 2-33: Secondary-data Packet Header                                                                    |     |

| Table 2-34: Secondary-data Packet Type                                                                      |     |

| Table 2-35: Header Bytes of InfoFrame Packet                                                                |     |

| Table 2-36: Header Bytes of Audio_TimeStamp Packet                                                          |     |

| Table 2-37: Examples of Maud and Naud Values                                                                |     |

| Table 2-38: Header Bytes of Audio_Stream Packet                                                             |     |

| Table 2-39: Audio_Stream Packet over the Main Link for One or Two Channel Audio                             |     |

| Table 2-40: Audio Stream Packet over the Main Link for Three to Eight Channel Audio                         |     |

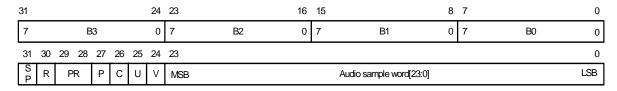

| Table 2-41: Bit Definition of the Payload of an Audio_Stream Packet with IEC60958-like Coding               |     |

| Table 2-42: Header Bytes of an Extension Packet                                                             |     |

| Table 2-43: Source AUX CH State and Event Descriptions                                                      |     |

| Table 2-44: Sink AUX CH State and Event Description                                                         |     |

| Table 2-45: Bit / Byte Size of Various Data Types of AUX CH Syntax                                          |     |

| Table 2-46: I <sup>2</sup> C Write Transaction Example 1                                                    |     |

| Table 2-47: I <sup>2</sup> C Write Transaction Method 1 with a Slow I <sup>2</sup> C Bus in the Sink Device |     |

| Table 2-48: I <sup>2</sup> C Write Transaction Method 2                                                     |     |

| Table 2-49: I <sup>2</sup> C Read Transaction Method 1                                                      |     |

| Table 2-50: I <sup>2</sup> C Read Transaction Example 2.                                                    |     |

| Table 2-51: I <sup>2</sup> C Write Followed by an I <sup>2</sup> C Read                                     |     |

| Table 2-52: Address Mapping for the DPCD (DisplayPort Configuration Data)                                   |     |

| Table 2-53: ANSI8B/10B Encoding and Scrambling Rules for Link Management                                    |     |

| Table 2-54: DisplayPort Address Mapping for Device Services                                                 |     |

| Table 3-1: DP_PWR Specification for Box-to-Box DisplayPort Connection                                       |     |

| Table 3-2: Hot Plug Detect Signal Specification                                                             |     |

| Table 3-3: DisplayPort AUX Channel Electrical Specifications                                                |     |

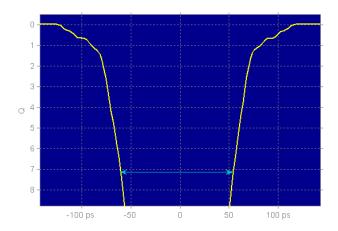

| Table 3-4: Mask Vertices for AUX CH at Transmitting IC Packages Pins (Informative)                          |     |

| Table 3-5: Mask Vertices for AUX CH at Connector Pins of Transmitting Device (Normative)                    |     |

| Table 3-6: Mask Vertices for AUX CH at Connector Pins of Receiving Device (Normative                        |     |

| Table 3-7: Mask Vertices for AUX CH at Receiving IC Packages Pins (Informative)                             |     |

| Table 3-8: ANSI 8B/10B Special Characters for DisplayPort Control Symbols                                   |     |

| Table 3-9: Symbol Patterns of Link Training                                                                 |     |

| Table 3-10: DisplayPort Main Link Transmitter (Main TX) Specifications                                      |     |

| Table 3-11: DisplayPort Main Link Receiver (Main RX) Specifications                                         |     |

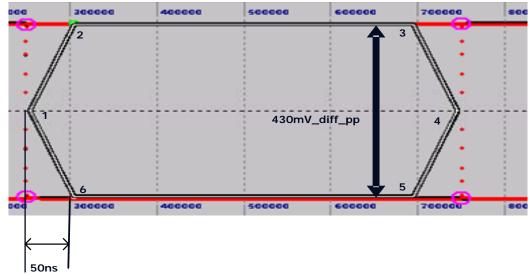

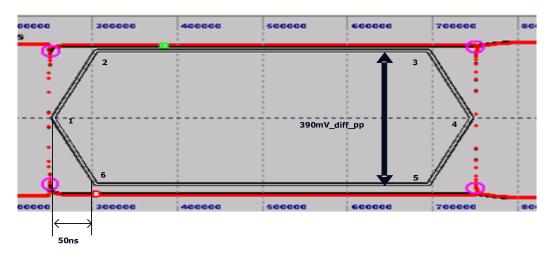

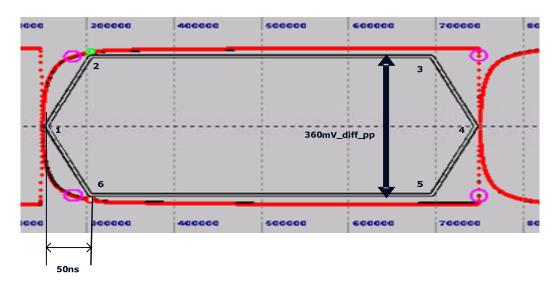

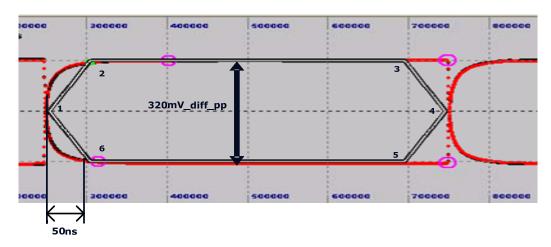

| Table 3-12: Allowed Vdiff_pp - Pre-emphasis Combinations                                                    |     |

| Table 3-13: Differential Noise Budget                                                                       |     |

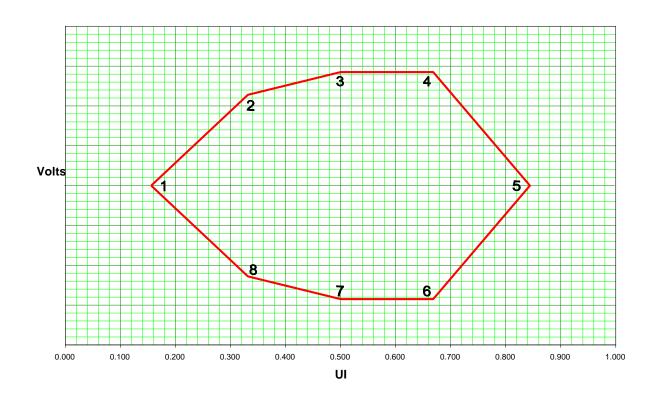

| Table 3-14: Mask Vertices for High Bit Rate                                                                 |     |

| Table 3-15: Mask Vertices for Reduced Bit Rate                                                              | 177 |

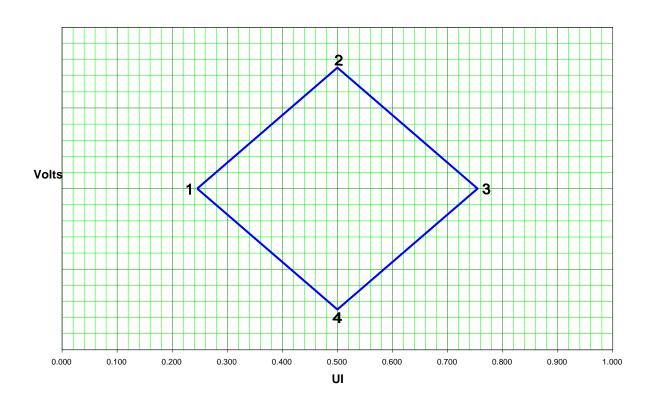

| Table 3-16: Sink EYE Vertices for TP3 at High Bit Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 178                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Table 3-17: Sink EYE Vertices at TP3 for Reduced Bit Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 179                                          |

| Table 3-18: TP3 EYE Mask Vertices at High Bit Rate for Embedded Connection (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 179                                          |

| Table 3-19: TP3 EYE Mask Vertices for Reduced Bit Rate for Embedded Connection (Informative)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 179                                          |

| Table 4-1: Impedance Profile Values for Cable Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 184                                          |

| Table 4-2: Mixed Mode Differential / Common relations of S-Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

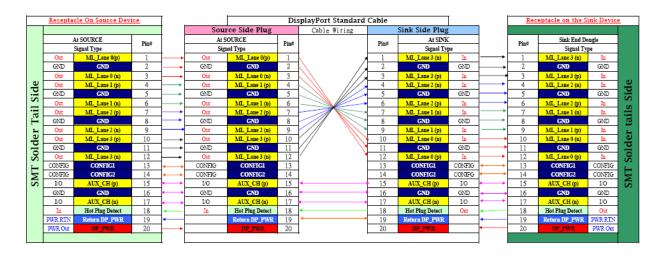

| Table 4-3: Source-Side Connector Pin Assignment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 195                                          |

| Table 4-4: Sink-Side Connector Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

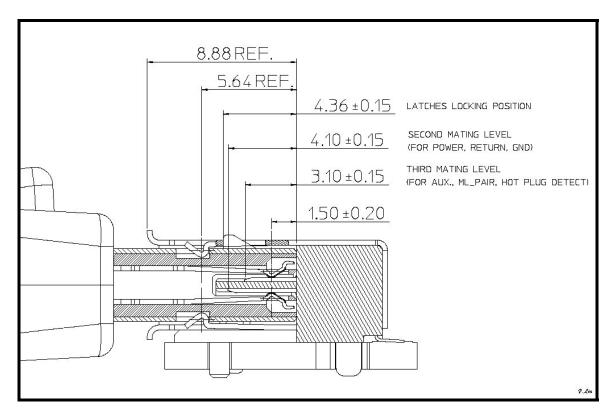

| Table 4-5: Mating Sequence Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

| Table 4-6: Connector Mechanical Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| Table 4-7: Connector Electrical Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| Table 4-8: Connector Environment Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| Table 4-9: DisplayPort Panel-side Internal Connector Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

| Table 4-10: Panel-side Connector Mechanical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| Table 4-11: Panel-side Connector Electrical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| Table 4-12: Panel-side Connector Environmental Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| Table 5-1: DisplayPort Colorimetry Format Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |

| Table 5-2: Required Lane Count for Typical TV Timings at Reduced Bit Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| Table 5-3: Required Lane Count for Typical Data Projector Timings at Reduced Bit Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| Table 5-4: DPCD Parameters Branch Device May Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

| Table 7-1: Channel to Speaker Mapping of Three Channel Audio with CA = 04h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| Table 10-1: Main Contributors to Version 1.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 237                                          |

| Table 10-2: Main Contributors to Version 1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 238                                          |

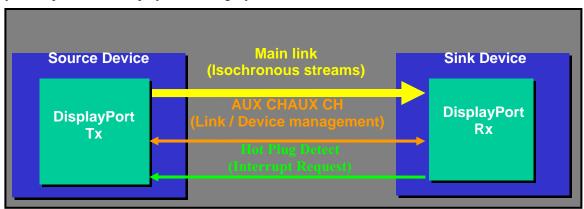

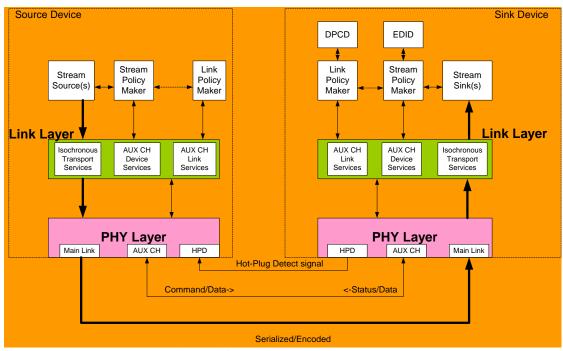

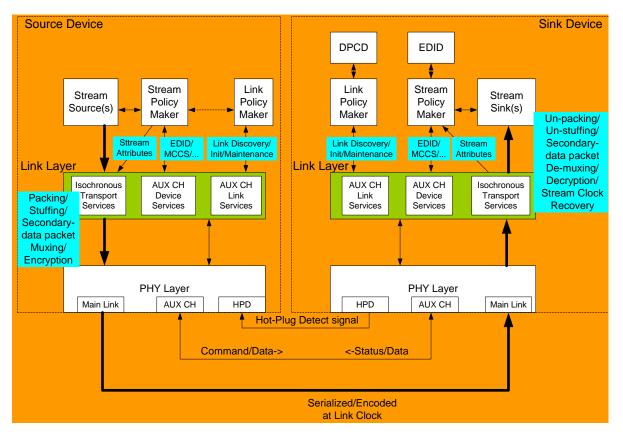

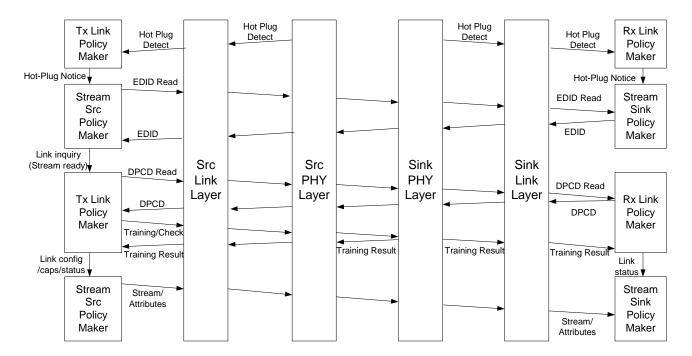

| Figure 1-1: DisplayPort Data Transport Channels  Figure 1-2: Layered Architecture  Figure 2-1: Overview of Link Layer Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                           |

| Figure 2-1: Overview of Link Layer Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

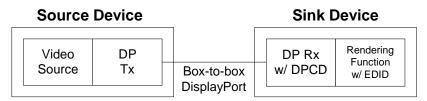

| Figure 2-2: Single Hop, Detachable DisplayPort Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

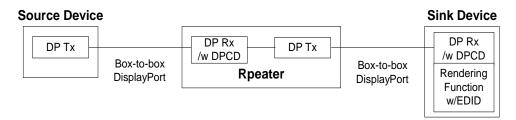

| Figure 2-4: DisplayPort Source Device to DisplayPort Sink Device via a Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |

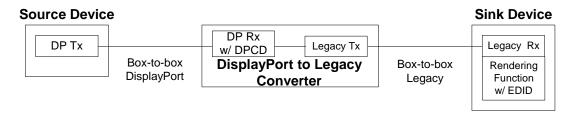

| Figure 2-5: Legacy Source Device to DisplayPort Sink Device via a Legacy to DisplayPort Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |

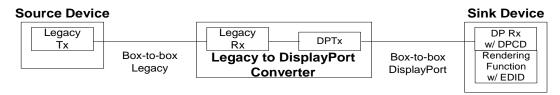

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                           |

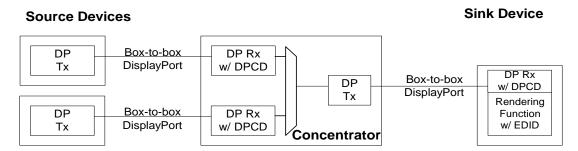

| Figure 7-6. Multiple Source Devices to a Sink Device via a Concentrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |

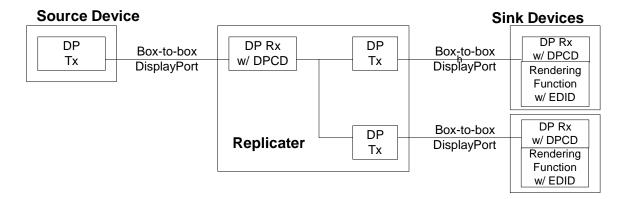

| Figure 2-6: Multiple Source Devices to a Sink Device via a Concentrator  Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36                                           |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                           |

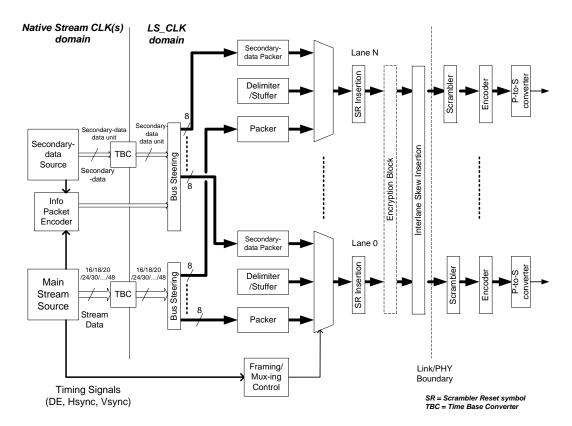

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>37                                     |

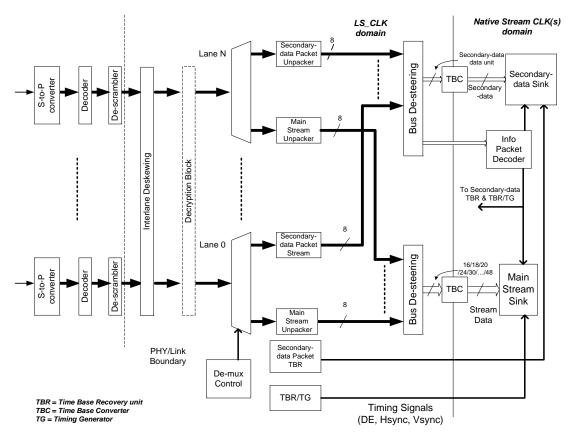

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>37<br>39                               |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>37<br>40                               |

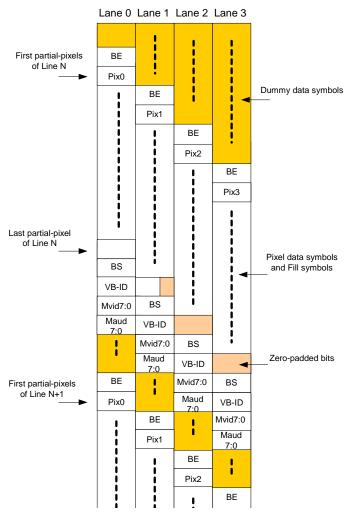

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>39<br>40<br>43                         |

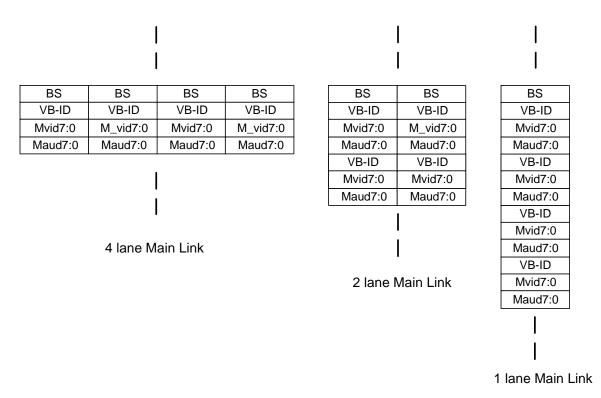

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>39<br>40<br>43                         |

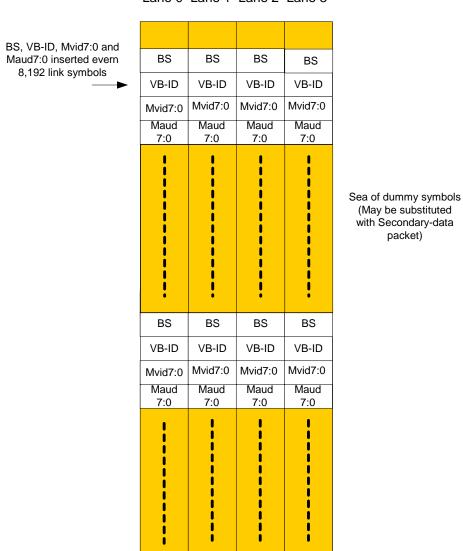

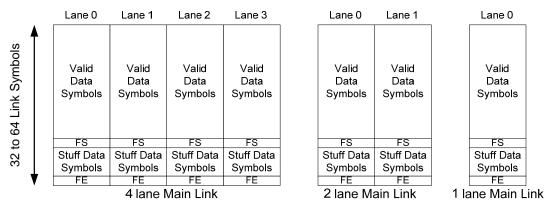

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>37<br>40<br>43<br>45                   |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit  Figure 2-14: Secondary Data Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36<br>37<br>39<br>40<br>45<br>45<br>59       |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36<br>37<br>40<br>43<br>45<br>59<br>62       |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit  Figure 2-14: Secondary Data Insertion  Figure 2-15: Inter-lane Skewing                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>37<br>40<br>45<br>46<br>59<br>62<br>63 |

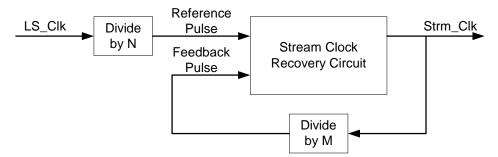

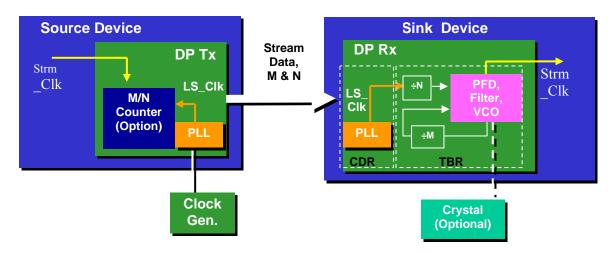

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit  Figure 2-14: Secondary Data Insertion  Figure 2-15: Inter-lane Skewing  Figure 2-16: Reference Pulse and Feedback Pulse of Stream Clock Recovery Circuit  Figure 2-17: M and N Value Determination in Asynchronous Clock Mode  Figure 2-18: Transport of DisplayPort_MainStream_Attribute.                                                                                                                                                                                    |                                              |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit  Figure 2-14: Secondary Data Insertion  Figure 2-15: Inter-lane Skewing  Figure 2-16: Reference Pulse and Feedback Pulse of Stream Clock Recovery Circuit  Figure 2-17: M and N Value Determination in Asynchronous Clock Mode                                                                                                                                                                                                                                                 |                                              |

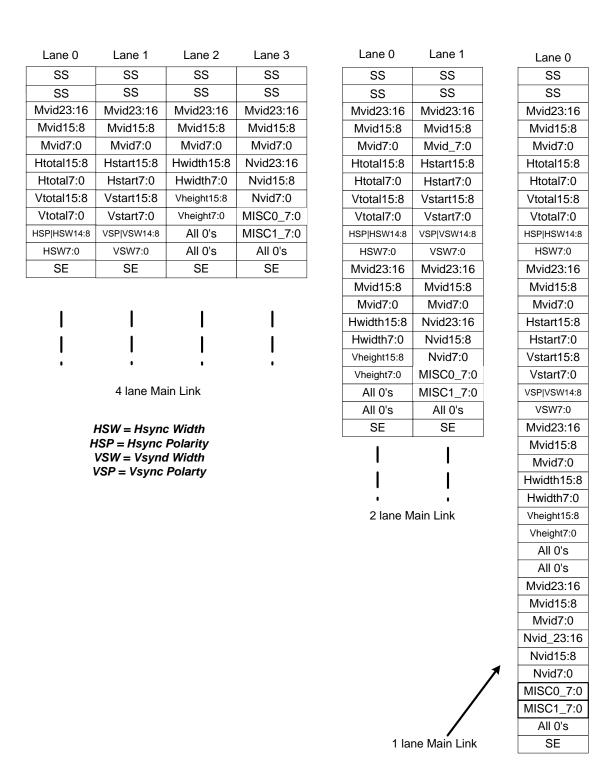

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link  Figure 2-13: Transfer Unit  Figure 2-14: Secondary Data Insertion  Figure 2-15: Inter-lane Skewing  Figure 2-16: Reference Pulse and Feedback Pulse of Stream Clock Recovery Circuit  Figure 2-17: M and N Value Determination in Asynchronous Clock Mode  Figure 2-18: Transport of DisplayPort_MainStream_Attribute.                                                                                                                                                                                    |                                              |

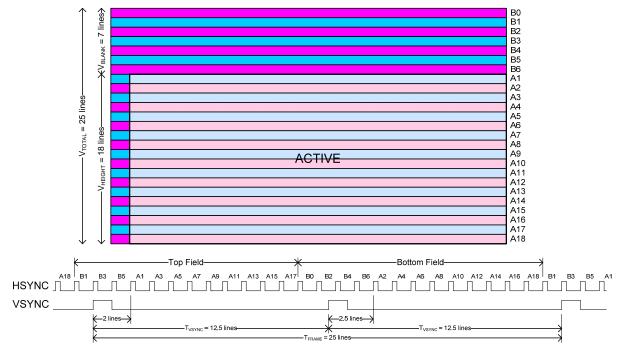

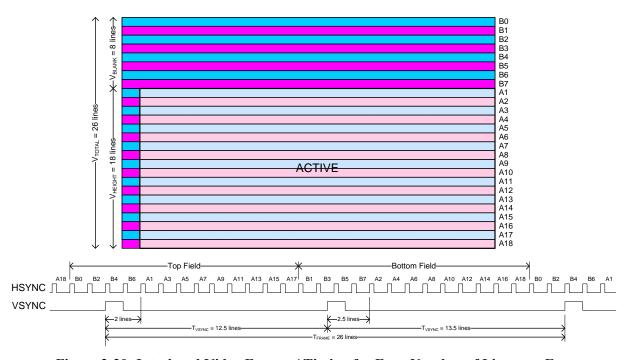

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link Figure 2-11: Link Symbols Over the Main Link without Main Video Stream Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link Figure 2-13: Transfer Unit Figure 2-14: Secondary Data Insertion Figure 2-15: Inter-lane Skewing Figure 2-16: Reference Pulse and Feedback Pulse of Stream Clock Recovery Circuit Figure 2-17: M and N Value Determination in Asynchronous Clock Mode Figure 2-18: Transport of DisplayPort MainStream Attribute Figure 2-19: Interlaced Video Format / Timing for Odd Number of Lines per Frame Figure 2-20: Interlaced Video Format / Timing for Even Number of Lines per Frame Figure 2-21: InfoFrame Packet |                                              |

| Figure 2-7: A Source Device to Multiple Sink Devices via a Replicator  Figure 2-8: High Level Block Diagram of Transmitter Main Link Data Path.  Figure 2-9: High Level Block Diagram of Receiver Main Link Data Path.  Figure 2-10: Main Video Stream Data Packing Example for a Four Lane Main Link.  Figure 2-11: Link Symbols Over the Main Link without Main Video Stream.  Figure 2-12: VB-ID, Mvid 7:0 and Maud 7:0 Packing Over the Main Link.  Figure 2-13: Transfer Unit.  Figure 2-14: Secondary Data Insertion.  Figure 2-15: Inter-lane Skewing.  Figure 2-16: Reference Pulse and Feedback Pulse of Stream Clock Recovery Circuit.  Figure 2-17: M and N Value Determination in Asynchronous Clock Mode.  Figure 2-18: Transport of DisplayPort_MainStream_Attribute.  Figure 2-19: Interlaced Video Format / Timing for Odd Number of Lines per Frame.  Figure 2-20: Interlaced Video Format / Timing for Even Number of Lines per Frame.     |                                              |

| Figure 2-24: Extension Packet Mapping over the Main Link                                                   |                       |

|------------------------------------------------------------------------------------------------------------|-----------------------|

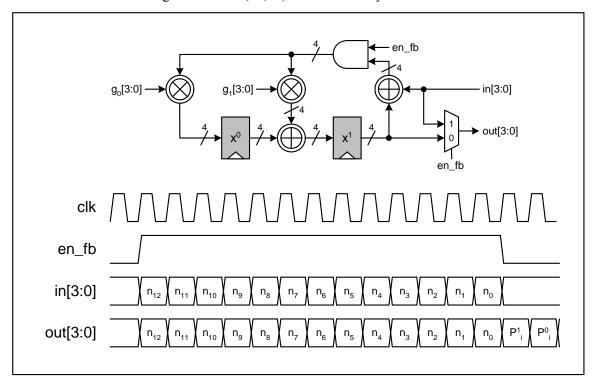

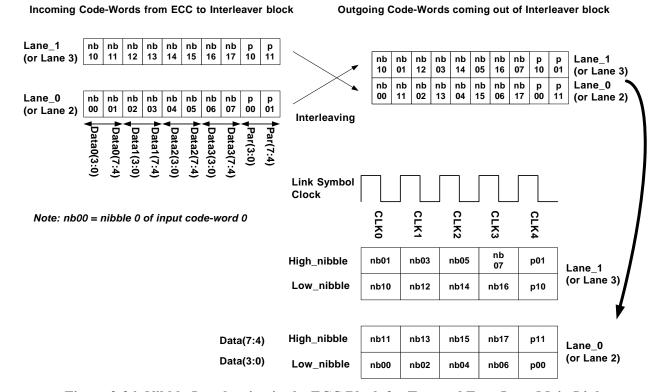

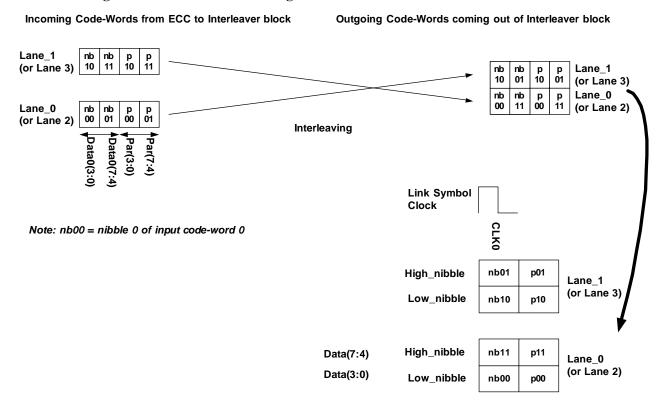

| Figure 2-26: Nibble-Interleaving in the ECC Block for Two and Four Lane Main Links                         |                       |

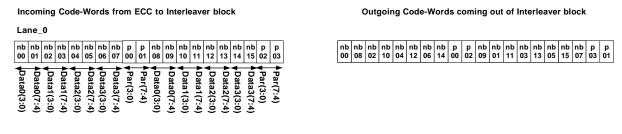

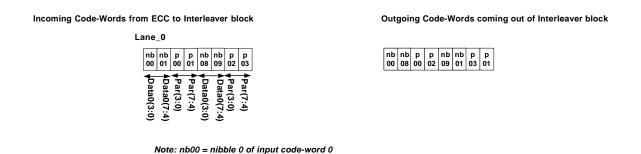

| Figure 2-27: Nibble-Interleaving in the ECC Block for a One Lane Main Link                                 |                       |

| Figure 2-28: Nibble-Interleaving in the ECC Block for Two and Four Lane Main Links (Header)                | 87                    |

| Figure 2-29: Nibble-Interleaving in the ECC Block for a One Lane Main Link (Header)                        | 87                    |

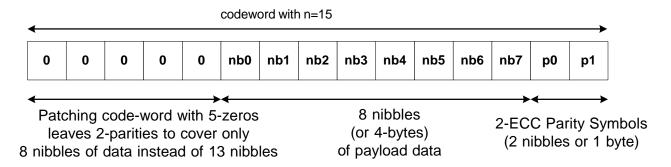

| Figure 2-30: Make-up of 15 Nibble Code Word for Packet Payload                                             |                       |

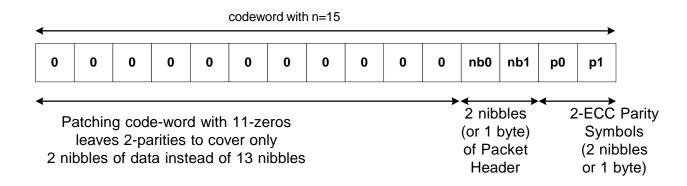

| Figure 2-31: Make-up of 15 Nibble Code Word for Packet Header                                              |                       |

| Figure 2-31: Make-up of 13 Nilotie Code Word for Facket Header                                             |                       |

| Figure 2-32: AUX CH Source State Diagram                                                                   |                       |

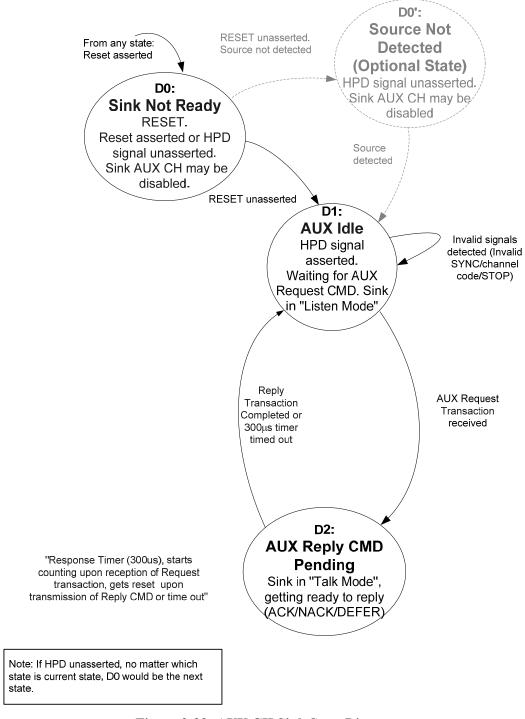

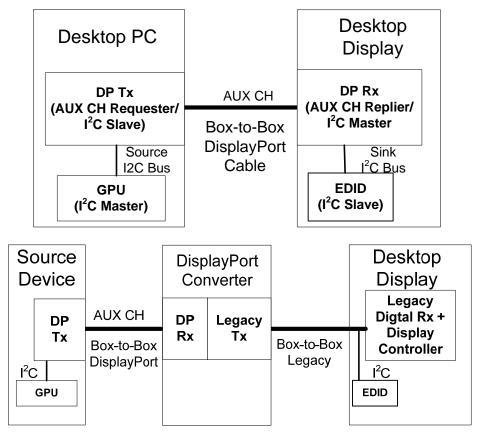

| Figure 2-33: AUX CH Shik State Diagram Figure 2-34: Examples of AUX CH Bridging Two I <sup>2</sup> C Buses | ۱۸۱<br>۱۸۱            |

| Figure 2-35: Action flow sequences of the Source upon Hot Plug Detect event (Informative)                  | 11ر<br>11ر            |

| Figure 2-35: Action now sequences of the Source upon 110t Fing Detect event (Informative)                  | 120                   |

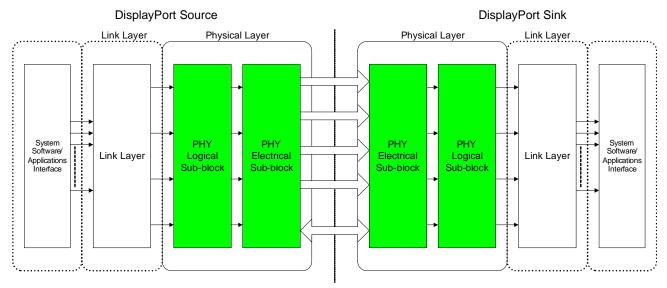

| Figure 3-1: DisplayPort Physical Layer                                                                     |                       |

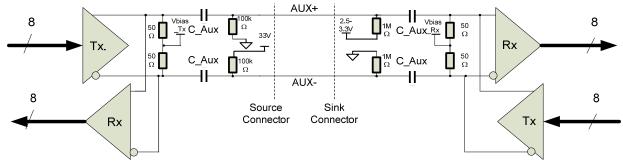

| Figure 3-1: Displayr Oit Filysical Layer  Figure 3-2: AUX CH Differential Pair                             |                       |

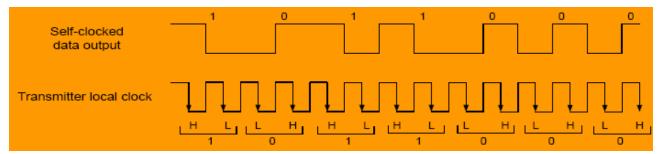

| Figure 3-3: Self-clocking with Manchester II coding                                                        |                       |

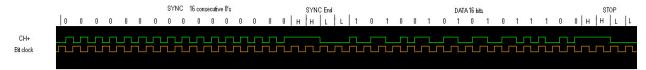

| Figure 3-3: Self-clocking with Malichester if couling                                                      |                       |

| Figure 3-5: AUX CH EYE Mask at Transmitting Integrated Circuit Package Pins (Informative)                  |                       |

| Figure 3-6: AUX CH EYE Mask at Transmitting Integrated Circuit Fackage Fins (Informative)                  |                       |

|                                                                                                            |                       |

| Figure 3-7: AUX CH EYE Mask at Connector Pins of Receiving Device (Normative)                              |                       |

| Figure 3-8: AUX CH EYE Mask at Receiving IC Package Pins (Informative)                                     |                       |

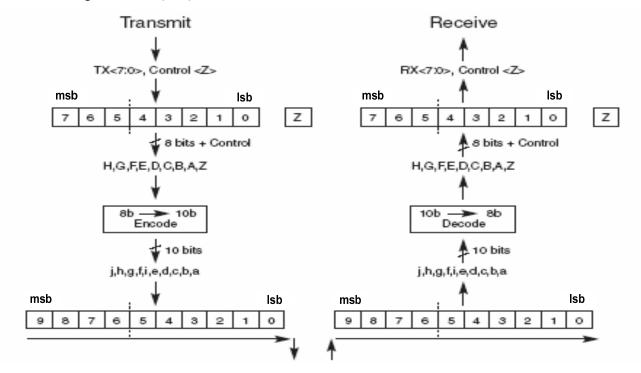

| Figure 3-9: Character to Symbol Mapping                                                                    |                       |

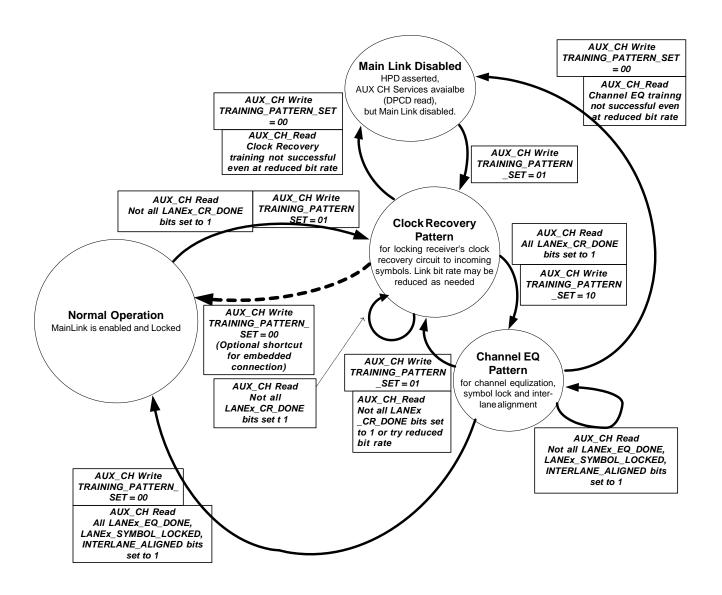

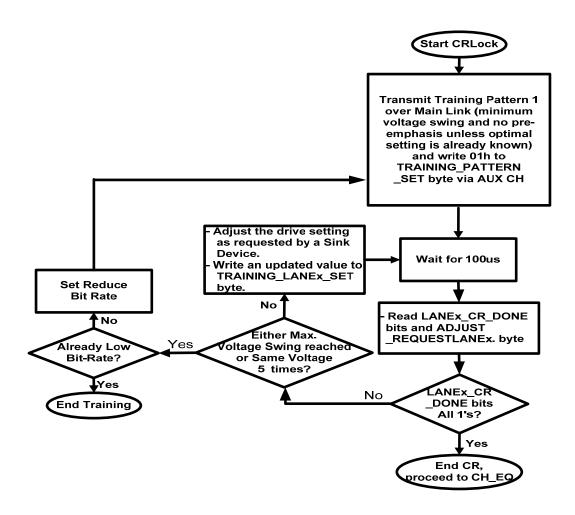

| Figure 3-10: Clock Recovery Sequence of Link Training                                                      |                       |

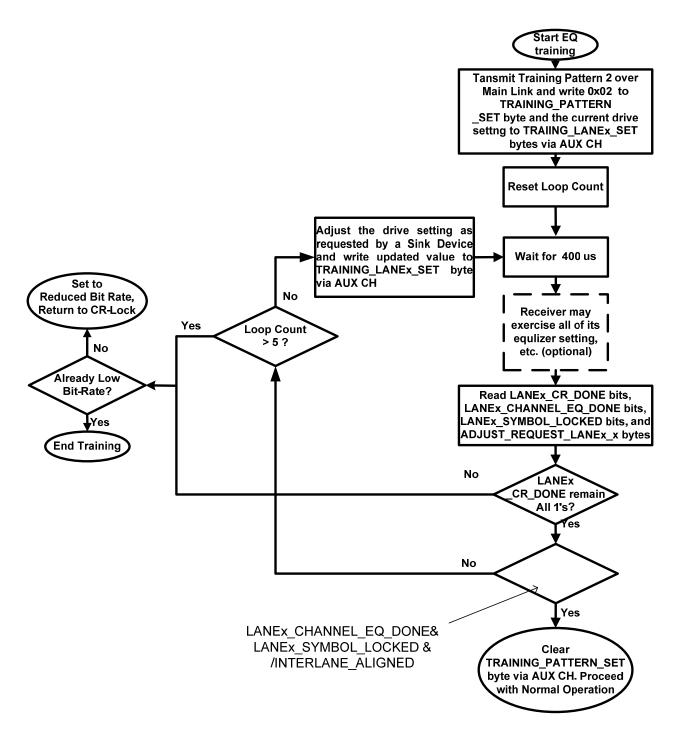

| Figure 3-11: Channel Equalization Sequence of Link Training                                                |                       |

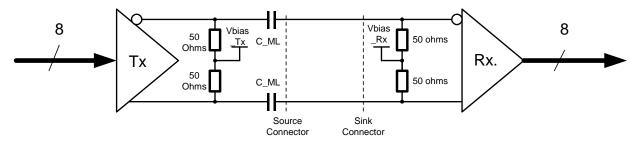

| Figure 3-12: Main Link Differential Pair                                                                   |                       |

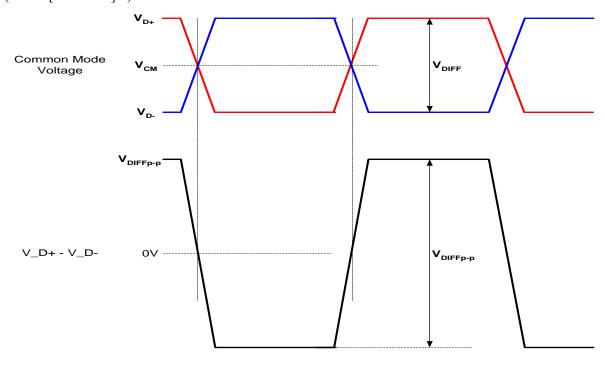

| Figure 3-13: Definition of Differential Voltage and Differential Voltage Peak-to-Peak                      |                       |

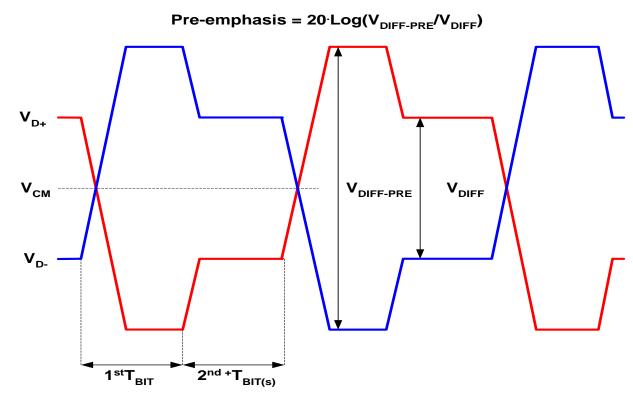

| Figure 3-14: Definition of Pre-emphasis                                                                    |                       |

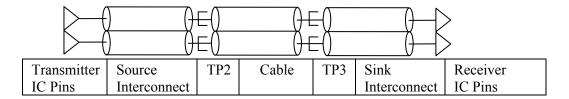

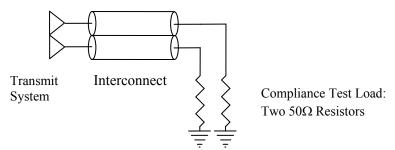

| Figure 3-15: Compliance Measurement Points of the Channel                                                  | 1 / I<br>1 <i>7</i> 1 |

|                                                                                                            |                       |

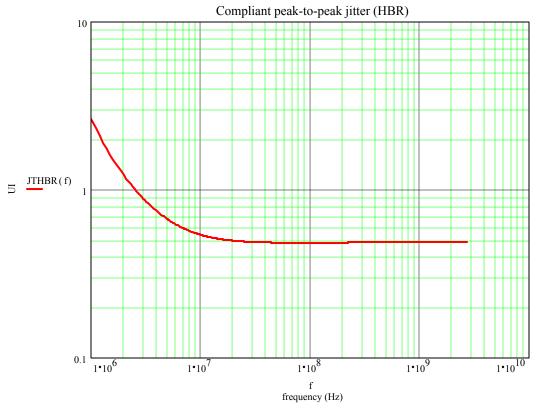

| Figure 3-17: High Bit Rate Jitter Output / Input Tolerance Mask                                            |                       |

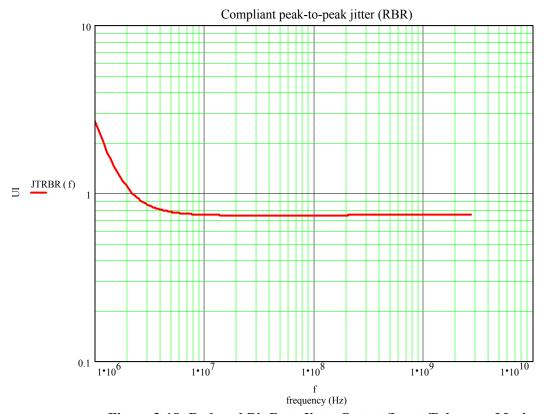

| Figure 3-18: Reduced Bit Rate Jitter Output / Input Tolerance Mask                                         |                       |

|                                                                                                            |                       |

| Figure 3-20: Mask at TP3                                                                                   |                       |

| Figure 4-1: Cable Assembly                                                                                 |                       |

| Figure 4-2: Bulk Cable Construction (Informative - for reference purpose only)                             |                       |

| Figure 4-3: Differential Impedance Profile Measurement Data Example                                        |                       |

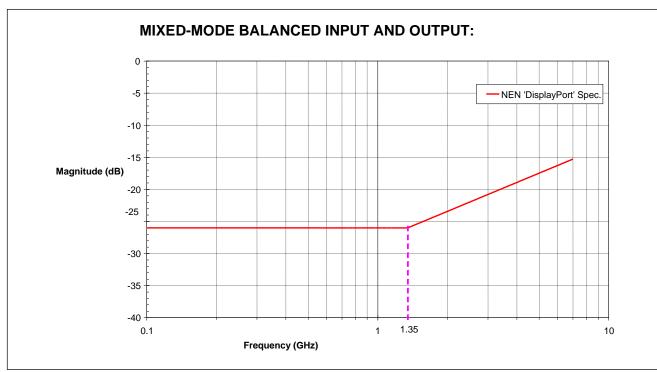

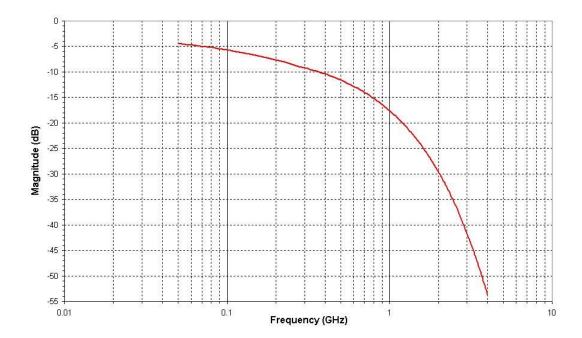

| Figure 4-4: Mixed Mode Differential Insertion Loss for High Bit Rate Cable Assembly                        |                       |

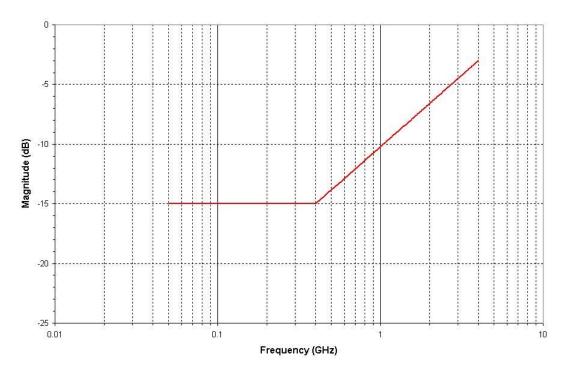

| Figure 4-5: Mixed Mode Differential Return Loss for High-bit-rate Cable Assembly                           |                       |

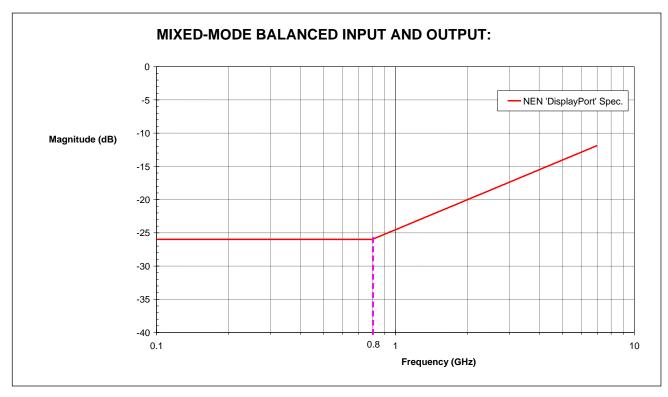

| Figure 4-6: Near End Total Noise (peak) for High-bit-rate Cable Assembly                                   |                       |

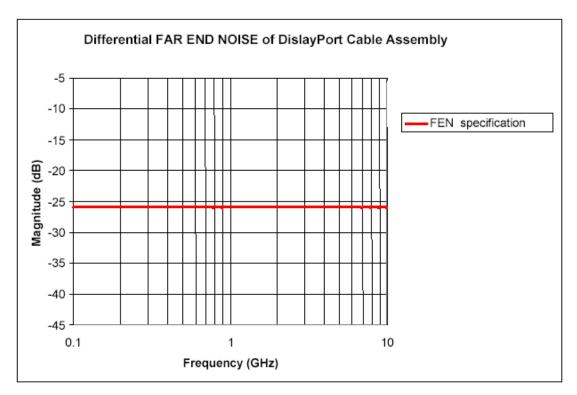

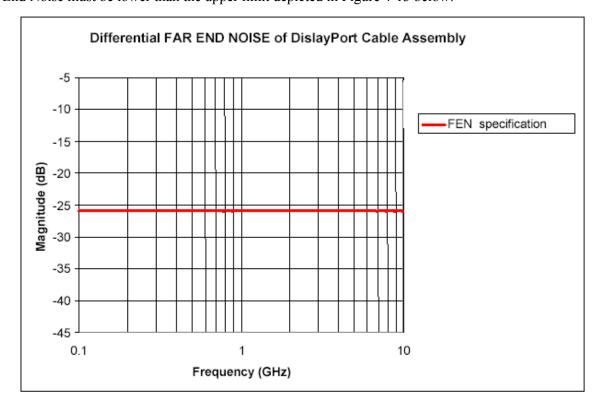

| Figure 4-7: Far End Total Noise (peak) for High Bit Rate Cable Assembly                                    |                       |

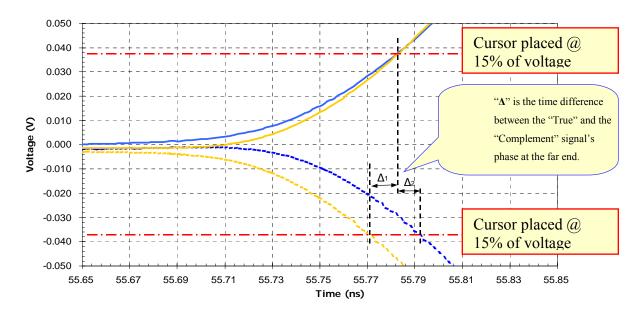

| Figure 4-8: Intra-Pair Skew Measurement Method                                                             |                       |

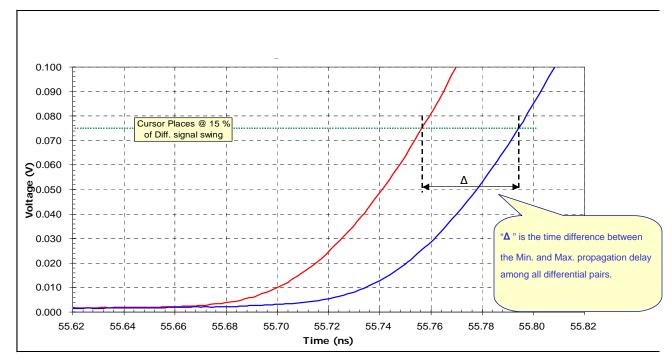

| Figure 4-9: Inter-Pair Skew Measurement Method                                                             |                       |

| Figure 4-10: Mixed Mode Differential Insertion Loss (SDD21) Mask of Reduced Bit Rate Cable                 |                       |

| Figure 4-11: Mixed Mode Differential Return Loss (SDD11) of reduced Bit Rate Cable                         |                       |

| Figure 4-12: Near End Total Noise (peak) for Reduced Bit Rate Cable Assembly                               |                       |

| Figure 4-13: Far End Total Noise (peak) for Reduced Bit Rate Cable Assembly                                |                       |

| Figure 4-14: External Cable Connector Assembly Wiring                                                      |                       |

| Figure 4-15: Connector Mating Levels                                                                       |                       |

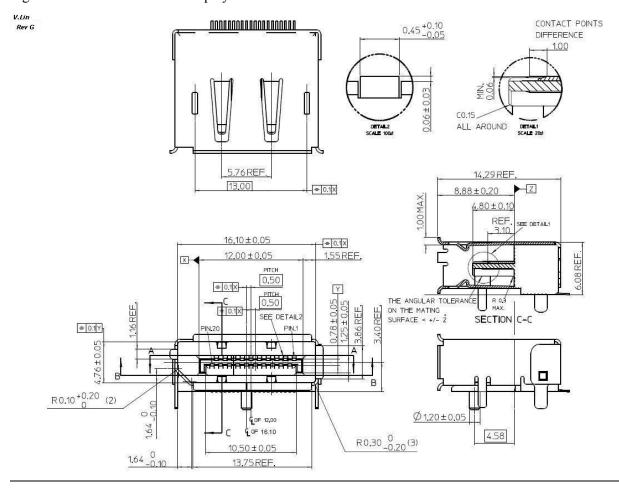

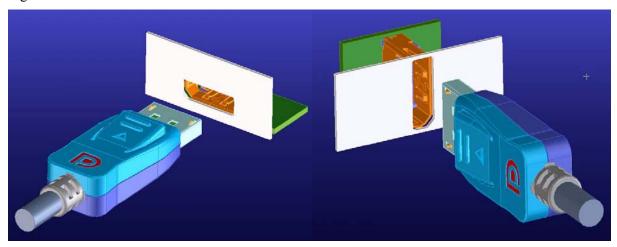

| Figure 4-16: DisplayPort External Connector Drawings                                                       |                       |

| Figure 4-17: DisplayPort External Cable-Connector Assembly Drawings                                        |                       |

| Figure 4-18: Recommended Orientation of External Connector                                                 |                       |

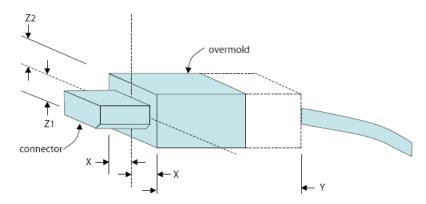

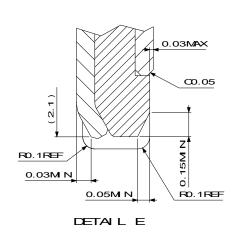

| Figure 4-19: Plug Over-Mold Dimensions for Non-Latch Plug Connector                                        | 203                   |

| Figure 4-20: Fully-mated Condition for DisplayPort External Connectors                           | 204 |

|--------------------------------------------------------------------------------------------------|-----|

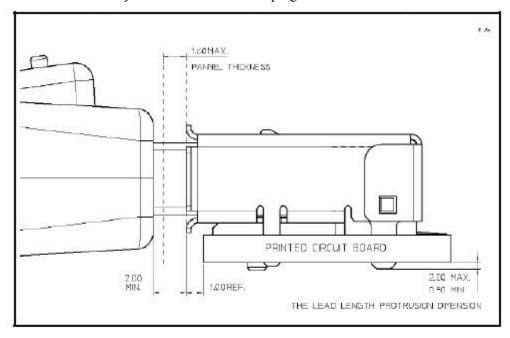

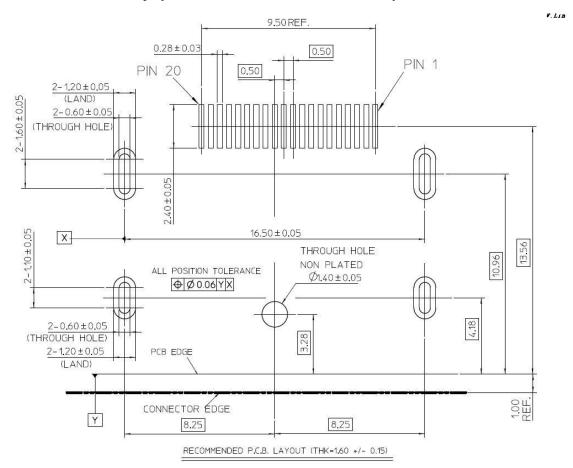

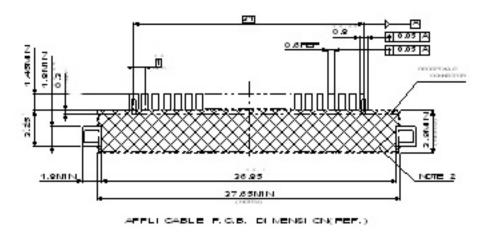

| Figure 4-21: Recommended PCB Layout for DisplayPort External Connector                           | 205 |

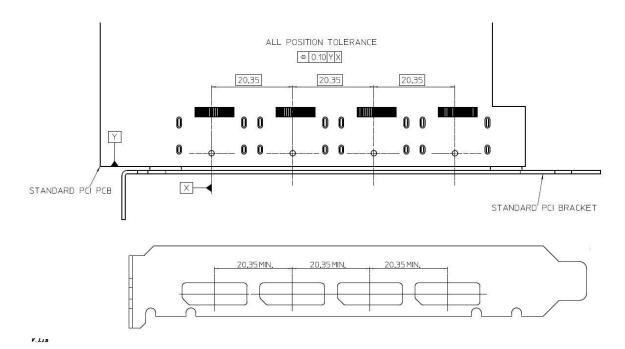

| Figure 4-22: Reference Design for Four DisplayPort External Connectors on a PCI Card             | 206 |

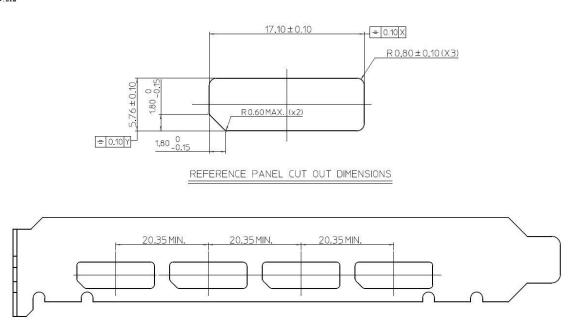

| Figure 4-23: Panel Cut Out Reference Dimensions                                                  | 206 |

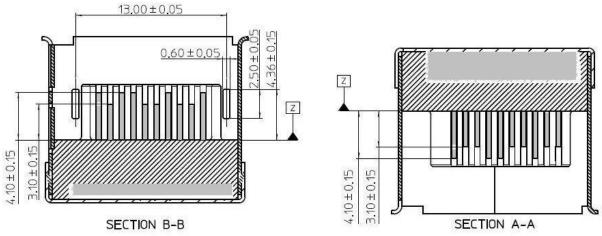

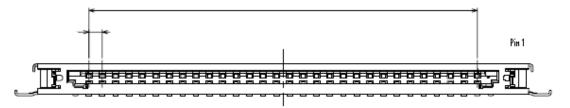

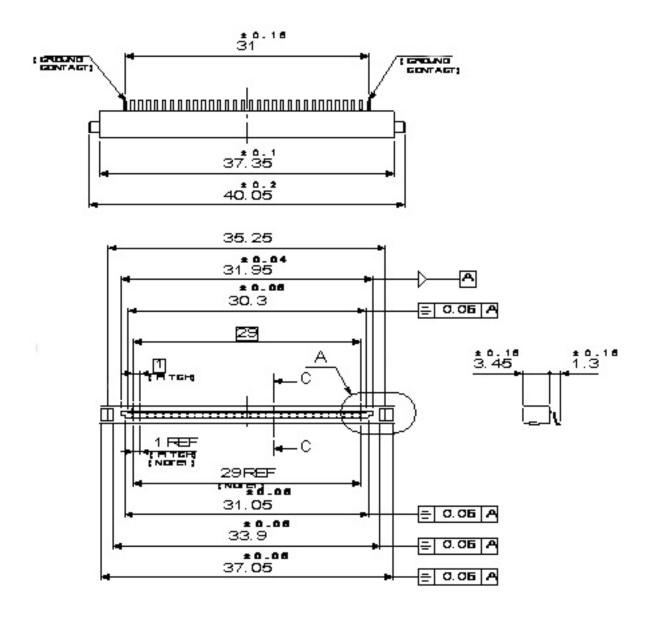

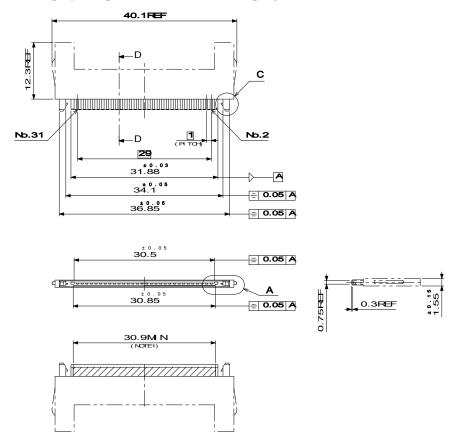

| Figure 4-24: Panel-side Internal PCB Mount Receptacle Connector with Pin 1 Shown                 | 208 |

| Figure 4-25: Panel-side Internal PCB Mount Receptacle Connector (in unit of mm)                  | 210 |

| Figure 4-26: PCB Mount Connector Recommended Footprint Layout (in unit of mm)                    | 211 |

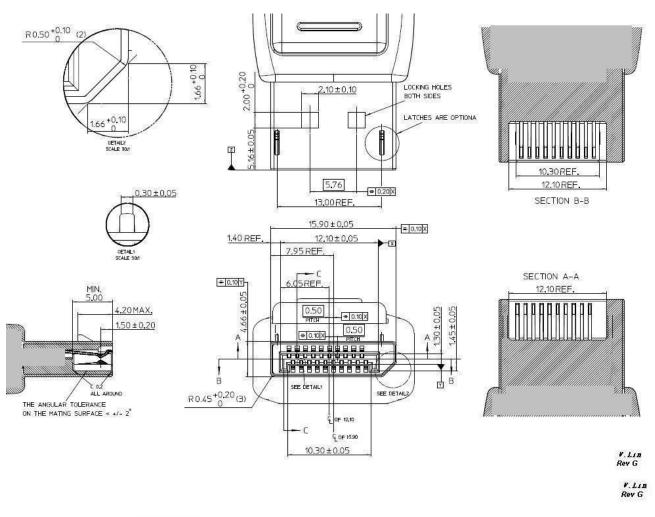

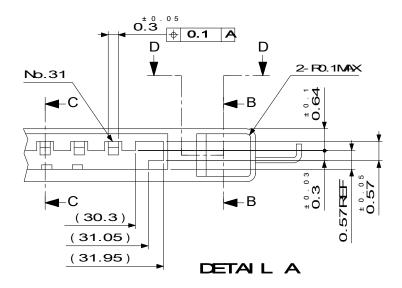

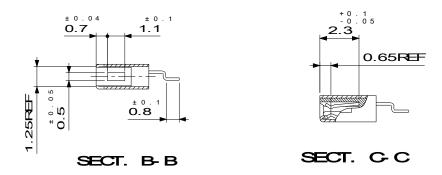

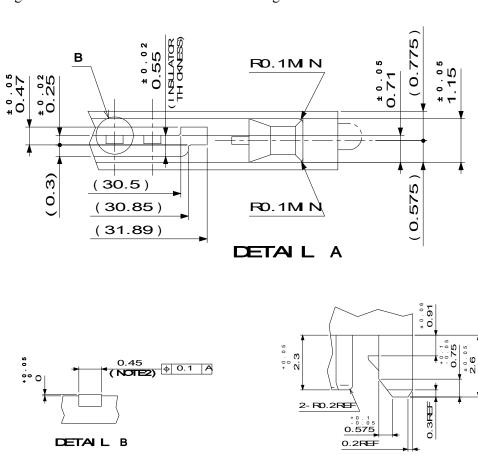

| Figure 4-27: Panel-side Internal Cable Plug Connector (in unit of mm)                            | 211 |

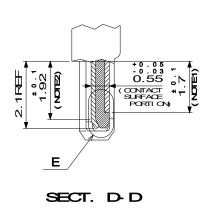

| Figure 4-28: Contact and Mechanical Guide Details (in unit of mm)                                | 212 |

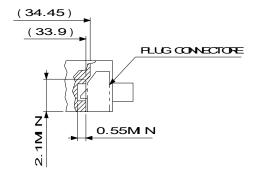

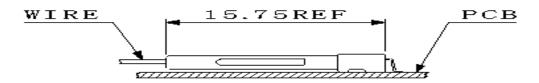

| Figure 4-29: Mating Condition (Reference) of Panel Side Internal Cable Connector (in unit of mm) | 213 |

| Figure 5-1: HPD Events                                                                           | 219 |

| Figure 5-2: Action Flow upon Addition of Sink Device                                             | 226 |

| Figure 7-1: Audio Stream Packets Transfer with No Video or During Video Vertical Blanking        | 230 |

| Figure 7-2: Audio Stream Packets Transfer Along with Video during Video Vertical Active Period   | 230 |

#### Preface

## **Intellectual Property**

Copyright © 2006-2008 Video Electronics Standards Association. All rights reserved.