E-DDC TM

510 651 5127

Phone: 510 651 5122

39899 Balentine Drive, Suite 125 Newark, CA 94560

# VESA Enhanced Display Data Channel (EDDC) Standard

#### Version 1.2

**December 26, 2007**

## **Purpose**

The purpose of this standard is to define a communications channel between an electronic display (e.g. a CRT, LCD, etc display) and a host system. The channel may be used to carry configuration information to enable 'plug & play' and allow optimum use of the display. The channel may also carry display control information.

## Summary

Today's computing and consumer electronic environments demands that systems offer user-friendly setup. With the growing popularity of intuitive and simpler software user interfaces, hardware manufacturers are responding with plug-and-play systems and peripherals. However, for the user to receive full benefit from these advances, standardization is necessary. VESA, as the prominent standards organization for graphics subsystems, has developed a communications channel between the host and the display. This communication channel offers basic configuration information plus a standard way of communicating advanced functionality

#### Errata or SCRs published

Adopted April 19, 2013: E-DDC Address Update NXP v2

# 1 Summary of the Proposed Change(s) for E-DDC Address Update SCR

The list of devices that can be connected to the same I<sup>2</sup>C / DDC bus doesn't reflect all the modules we have today on DDC bus in HDMI and DisplayPort systems.

## 1.1 IPR (Intellectual Property Rights) declaration, if any

N/A

### 1.2 Benefits as a Result of the Changes

Avoid conflict with other devices connected on the I<sup>2</sup>C / DDC bus.

# 1.3 Assessment of the Impact

It's just a clarification of slave addresses already allocated by other specifications using the Display Data Channel.

No change of features, protocol or electrical specification.

#### 1.4 Analysis of the Device Hardware Implication

The hardware implementation is mandatory by the other specifications, so the slave address allocation is already done as soon as the product respects the features of the corresponding specification.

About conflict between Audio Processor and DisplayPort Dual-Mode Video Adaptor, these are not expected to co-exist on the same physical DDC bus in practice.

## 1.5 Analysis of the Device Software Implications

No software change is needed.

# 1.6 Analysis of the Compliance Test & Interop Implications

Already tested in different Compliance Tests (HDMI, HDCP, DP, DP Dual Mode).

#### 1.7 New Referenced Documents Resulting from Change

- 1. High-bandwidth Digital Content Protection System Revision 1.4, July 2009.

- 2. VESA DisplayPort Dual-Mode Standard Version 1, February 2012.

- 3. High-Definition Multimedia Interface specification Version 2.0, March 2013.

- 4. Display Data Channel Command Interface Standard Version 1.1, Oct 29, 2004.

## 2 Proposed Document Change(s) or Addition(s)

This section captures the list of proposed document changes in the specification.

# **2.2.2 Display Data Channel (DDC)**

A protocol based on I<sup>2</sup>C and used on a bi-directional data channel between the display and host. This protocol accesses devices at I<sup>2</sup>C addresses of A0h / A1h or A4h / A5h.

The DDC channel is used by HDMI, DP and DisplayPort Dual Mode standards for purposes beyond EDID data transport. The I<sup>2</sup>C slave/device addresses used by these standards are listed in Table 2-2. The intended purposes of these addresses are described in those respective standards.

# 2.2.3 DDC addresses (A0h / A1h and A4h / A5h)

Under DDC, each pair of I<sup>2</sup>C slave addresses (A0h/A1h and A4h/A5h) allows 256 bytes of data to be accessed. Larger data structures, up to 32K bytes, can be accessed using the E-DDC addressing technique – see section 2.2.4.

#### 2.2.3.1 Other DDC addresses

Table 2-2 lists the DDC/I<sup>2</sup>C addresses that are defined by DDC, HDMI, DP and DisplayPort Dual Mode standards.

I²C Slave AddressSpecification0x74h/75hReserved for HDCP (Primary Link Port) [1]0x76h/77hReserved for HDCP (Secondary Link Port) [1]0x80h/81hReserved for DisplayPort (Dual Mode Video Adaptor[2]0xA8h/A9hReserved for HDMI[3]0x6Eh/6FhReserved for DDC/CI Display for host communication (e.g. MCCS)[4]

**Table 2-2: Normative Addresses**

Note: Given that DisplayPort Dual Mode Video Adaptor uses the same Slave Address as that of Audio Processor, they can't co-exist on the same physical DDC bus.

E-DDC TM

Phone: 510 651 5122

510 651 5127

Fax:

39899 Balentine Drive, Suite 125 Newark, CA 94560

# **VESA Enhanced Display Data Channel (EDDC) Standard**

#### Version 1.2

## **December 26, 2007**

## **Purpose**

The purpose of this standard is to define a communications channel between an electronic display (e.g. a CRT, LCD, etc display) and a host system. The channel may be used to carry configuration information to enable 'plug & play' and allow optimum use of the display. The channel may also carry display control information.

## Summary

Today's computing and consumer electronic environments demands that systems offer user-friendly set-up. With the growing popularity of intuitive and simpler software user interfaces, hardware manufacturers are responding with plug-and-play systems and peripherals. However, for the user to receive full benefit from these advances, standardization is necessary. VESA, as the prominent standards organization for graphics subsystems, has developed a communications channel between the host and the display. This communication channel offers basic configuration information plus a standard way of communicating advanced functionality.

# **Table of Contents**

| Preface                                            |                          |

|----------------------------------------------------|--------------------------|

| e e                                                |                          |

| 1. Overview                                        |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    | on10                     |

|                                                    | 10                       |

| 2. Definitions                                     | 1                        |

| 2.1 Data formats                                   | 1                        |

|                                                    | n Data: E-EDID           |

|                                                    | n Data Extension Blocks1 |

|                                                    |                          |

|                                                    |                          |

| $2.2.1 I^2 C Bus$                                  |                          |

| 2.2.2 Display Data Channel (DDC)                   |                          |

| ,                                                  | n)                       |

| \ /                                                |                          |

|                                                    |                          |

|                                                    |                          |

| · · · · · · · · · · · · · · · · · · ·              |                          |

|                                                    |                          |

| _ :                                                |                          |

|                                                    |                          |

| _ ·                                                |                          |

| 3 31                                               |                          |

|                                                    |                          |

|                                                    |                          |

| 3. Co-existance of EDID and DisplayID Display Capa |                          |

| 3.1 Example of Host Operation                      | 18                       |

| 4. DDC/E-DDC - General                             |                          |

|                                                    |                          |

| <del>-</del>                                       |                          |

|                                                    |                          |

| _                                                  |                          |

| · · · · · · · · · · · · · · · · · · ·              |                          |

|                                                    |                          |

|                                                    | 20                       |

|                                                    | ID:                      |

| 5.1.2 Basic Operation for E-DDC Access of Dis      | splayID:2                |

| 6. Command Structures                              |                          |

| 6.1 Read at the Current Address                    | 22                       |

|                                                    | 24                       |

|                                                    |                          |

| 6.4       E-DDC Random Read Operation       2.0         6.5       E-DDC Sequential Read Operation       2.0         7.       Physical Connections – Video Interfaces       2.2         7.1       VGA       2.2         7.1.1       Mechanical       2.2         7.1.2       VGA Connector Pinouts       2.2         7.1.3       Power requirements       2.2         7.2.1       Mechanical       3.         7.2.1       Mechanical       3.         7.2.2       Connector Pin-out       3.         7.2.3       Power Requirements       3.         7.3       High Bandwidth Digital Multimedia Interface (HDMI)       3.         7.3.1       Mechanical – HDMI-A       3.         7.3.2       Mechanical – HDMI-B       3.         7.3.3       HDMI Connector Pin-outs       3.         7.3.4       Power Requirements       3.         7.4       DisplayPort       3.         7.4.1       Mechanical – External DisplayPort       3.         7.4.2       DisplayPort External Connector Pin-Out       3.         7.4.3       Power Requirements       3.         8.       DisplayPort and DDC/E-DDC       3.         9.                                                                                                                                                                                  | 6.  | .3 D               | DC Sequential Read Operation                        | 24 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----------------------------------------------------|----|

| 7. Physical Connections – Video Interfaces       2:         7.1. VGA       2:         7.1.1 Mechanical       2:         7.1.2 VGA Connector Pinouts       2:         7.1.3 Power requirements       2         7.2 Digital Visual interface (DVI)       2:         7.2.1 Mechanical       3:         7.2.2 Connector Pin-out       3:         7.2.3 Power Requirements       3         7.3.1 Mechanical – HDMI-A       3.         7.3.2 Mechanical – HDMI-B       3.         7.3.3 HDMI Connector Pin-outs       3.         7.3.4 Power Requirements       3.         7.4.1 Mechanical – External DisplayPort       3.         7.4.2 DisplayPort External Connector Pin-Out       3.         7.4.3 Power Requirements       3.         8. DisplayPort and DDC/E-DDC       3.         9. Enhanced DDC System/Display Combinations       3.         9.1 Interoperability       3.         9.1.2 Enhanced DDC Host System Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host System Connected to a DDC Display       3.         10.1 Older Designs       3.         10.2 New Display Designs       3.         10.3 New Host Subsystem Designs       3.         10.4 12 C Bus       3.                                                                                                      | 6.  |                    |                                                     |    |

| 7.1.1 VGA       22         7.1.2 VGA Connector Pinouts       2         7.1.3 Power requirements       2         7.2 Digital Visual interface (DVI)       2         7.2.1 Mechanical       3         7.2.2 Connector Pin-out       3         7.2.3 Power Requirements       3         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A       3         7.3.2 Mechanical – HDMI-B       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.2 Enhanced DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.4 1°C Bus       3         10.5 E-DDC Unique Features       3         10.5.1 S                                                                                                                       | 6.  | .5 E-              | DDC Sequential Read Operation                       | 27 |

| 7.1.1 Mechanical       2.         7.1.2 VGA Connector Pinouts       2.         7.1.3 Power requirements       2.         7.2 Digital Visual interface (DVI)       2.         7.2.1 Mechanical       3.         7.2.2 Connector Pin-out       3.         7.2.3 Power Requirements       3.         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3.         7.3.1 Mechanical – HDMI-4       3.         7.3.2 Mechanical – HDMI-B       3.         7.3.3 HDMI Connector Pin-outs       3.         7.3.4 Power Requirements       3.         7.4 DisplayPort       3.         7.4.1 Mechanical – External DisplayPort       3.         7.4.2 DisplayPort External Connector Pin-Out       3.         7.4.3 Power Requirements       3.         8. DisplayPort and DDC/E-DDC       3.         9. Enhanced DDC System/Display Combinations       3.         9.1 Interoperability       3.         9.1.1 DDC Host System Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host Connected to a DDC Display       3.         10.1 Older Designs       3.         10.2 New Display Designs       3.         10.3 New Host                                                                                    | 7.  | Physic             | al Connections – Video Interfaces                   | 28 |

| 7.1.1 Mechanical       2.         7.1.2 VGA Connector Pinouts       2.         7.1.3 Power requirements       2.         7.2 Digital Visual interface (DVI)       2.         7.2.1 Mechanical       3.         7.2.2 Connector Pin-out       3.         7.2.3 Power Requirements       3.         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3.         7.3.1 Mechanical – HDMI-4       3.         7.3.2 Mechanical – HDMI-B       3.         7.3.3 HDMI Connector Pin-outs       3.         7.3.4 Power Requirements       3.         7.4 DisplayPort       3.         7.4.1 Mechanical – External DisplayPort       3.         7.4.2 DisplayPort External Connector Pin-Out       3.         7.4.3 Power Requirements       3.         8. DisplayPort and DDC/E-DDC       3.         9. Enhanced DDC System/Display Combinations       3.         9.1 Interoperability       3.         9.1.1 DDC Host System Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host Connected to a DDC Display       3.         10.1 Older Designs       3.         10.2 New Display Designs       3.         10.3 New Host                                                                                    | 7.  | .1 V               | GA                                                  | 28 |

| 7.1.2 VGA Connector Pinouts       2         7.1.3 Power requirements       2         7.2 Digital Visual interface (DVI)       2         7.2.1 Mechanical       3         7.2.2 Connector Pin-out       3         7.2.3 Power Requirements       3         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A       3         7.3.2 Mechanical – HDMI-B       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort External Connector Pin-Out       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.1 DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4                                                                                                      |     |                    |                                                     |    |

| 7.2 Digital Visual interface (DVI)       22         7.2.1 Mechanical       3         7.2.2 Connector Pin-out       3         7.2.3 Power Requirements       3         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A       3         7.3.2 Mechanical – HDMI-B       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort External Connector Pin-Out       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.2 Enhanced DDC Host System Connected to an E-DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/CI and                                                                                     |     | 7.1.2              |                                                     |    |

| 7.2 Digital Visual interface (DVI)       22         7.2.1 Mechanical       3         7.2.2 Connector Pin-out       3         7.2.3 Power Requirements       3         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A       3         7.3.2 Mechanical – HDMI-B       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort External Connector Pin-Out       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.2 Enhanced DDC Host System Connected to an E-DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/CI and                                                                                     |     | 7.1.3              | Power requirements                                  | 29 |

| 7.2.2 Connector Pin-out       3         7.2.3 Power Requirements       3         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A       3         7.3.2 Mechanical – HDMI-B       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4 DisplayPort       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort External Connector Pin-Out       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.1 DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4         11. Appendix A: Answers to Commonly Asked Questio                                                                                    | 7.  | .2 Di              | igital Visual interface (DVI)                       | 29 |

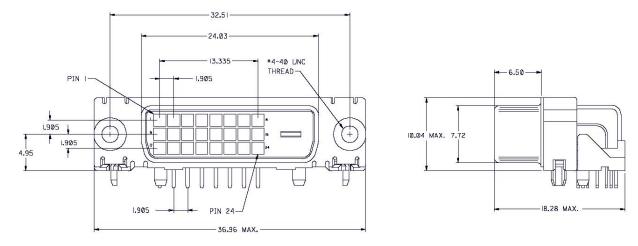

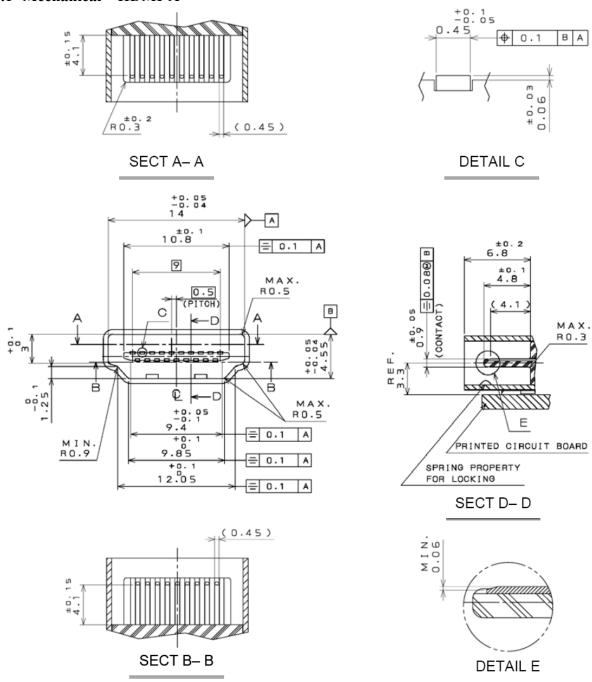

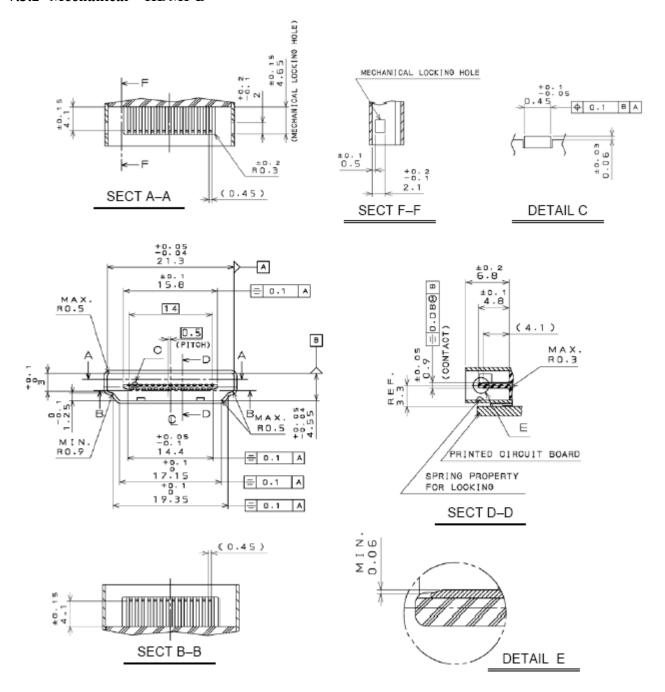

| 7.2.3 Power Requirements       3         7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 7.2.1              | Mechanical                                          | 30 |

| 7.3 High Bandwidth Digital Multimedia Interface (HDMI)       3         7.3.1 Mechanical – HDMI-A.       3         7.3.2 Mechanical – HDMI-B.       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4.1 DisplayPort       3         7.4.2 DisplayPort External DisplayPort.       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.1 DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4         11. Appendix A: Answers to Commonly Asked Questions       4 </td <td></td> <td>7.2.2</td> <td>Connector Pin-out</td> <td>31</td> |     | 7.2.2              | Connector Pin-out                                   | 31 |

| 7.3.1 Mechanical – HDMI-A.       3.         7.3.2 Mechanical – HDMI-B.       3.         7.3.3 HDMI Connector Pin-outs.       3.         7.3.4 Power Requirements.       3.         7.4 DisplayPort       3.         7.4.1 Mechanical – External DisplayPort.       3.         7.4.2 DisplayPort External Connector Pin-Out.       3.         7.4.3 Power Requirements.       3.         8. DisplayPort and DDC/E-DDC.       3.         9. Enhanced DDC System/Display Combinations.       3.         9.1 Interoperability.       3.         9.1.1 DDC Host System Connected to an E-DDC Display.       3.         9.1.2 Enhanced DDC Host Connected to a DDC Display.       3.         10. E-DDC Compliance.       3.         10.1 Older Designs.       3.         10.2 New Display Designs.       3.         10.3 New Host Subsystem Designs.       3.         10.5 E-DDC Unique Features.       3.         10.5.1 Segment Pointer.       3.         10.5.2 Power Pin.       4.         10.5.3 EDID / DisplayID Available with Display Powered Off       4.         10.6 Co-existence of E-DDC, DDC/CI and HDCP.       4.         11. Appendix A: Answers to Commonly Asked Questions.       4.                                                                                                           |     |                    |                                                     |    |

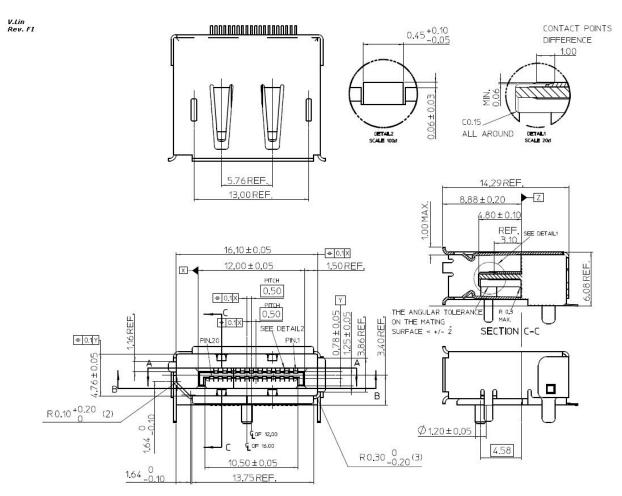

| 7.3.2 Mechanical – HDMI-B       3         7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4 DisplayPort       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort External Connector Pin-Out       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.1 DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                 | 7.  | .3 Hi              |                                                     |    |

| 7.3.3 HDMI Connector Pin-outs       3         7.3.4 Power Requirements       3         7.4 DisplayPort       3         7.4.1 Mechanical – External DisplayPort       3         7.4.2 DisplayPort External Connector Pin-Out       3         7.4.3 Power Requirements       3         8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.1 DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                           |     | 7.3.1              |                                                     |    |

| 7.3.4 Power Requirements       3.         7.4 DisplayPort       3.         7.4.1 Mechanical – External DisplayPort       3.         7.4.2 DisplayPort External Connector Pin-Out       3.         7.4.3 Power Requirements       3.         8. DisplayPort and DDC/E-DDC       3.         9. Enhanced DDC System/Display Combinations       3.         9.1 Interoperability       3.         9.1.1 DDC Host System Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host Connected to a DDC Display       3.         10. E-DDC Compliance       3.         10.1 Older Designs       3.         10.2 New Display Designs       3.         10.3 New Host Subsystem Designs       3.         10.5 E-DDC Unique Features       3.         10.5.1 Segment Pointer       3.         10.5.2 Power Pin       4.         10.5.3 EDID / DisplayID Available with Display Powered Off       4.         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4.         11. Appendix A: Answers to Commonly Asked Questions       4.                                                                                                                                                                                                                                                                     |     |                    |                                                     |    |

| 7.4 DisplayPort       3.         7.4.1 Mechanical – External DisplayPort       3.         7.4.2 DisplayPort External Connector Pin-Out       3.         7.4.3 Power Requirements       3.         8. DisplayPort and DDC/E-DDC       3.         9. Enhanced DDC System/Display Combinations       3.         9.1 Interoperability       3.         9.1.1 DDC Host System Connected to an E-DDC Display       3.         9.1.2 Enhanced DDC Host Connected to a DDC Display       3.         10. E-DDC Compliance       3.         10.1 Older Designs       3.         10.2 New Display Designs       3.         10.3 New Host Subsystem Designs       3.         10.5 E-DDC Unique Features       3.         10.5.1 Segment Pointer       3.         10.5.2 Power Pin       4.         10.5.3 EDID / DisplayID Available with Display Powered Off       4.         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4.         11. Appendix A: Answers to Commonly Asked Questions       4.                                                                                                                                                                                                                                                                                                               |     |                    |                                                     |    |

| 7.4.1       Mechanical – External DisplayPort       3.         7.4.2       DisplayPort External Connector Pin-Out       3.         7.4.3       Power Requirements       3.         8.       DisplayPort and DDC/E-DDC       3.         9.       Enhanced DDC System/Display Combinations       3.         9.1       Interoperability       3.         9.1.1       DDC Host System Connected to an E-DDC Display       3.         9.1.2       Enhanced DDC Host Connected to a DDC Display       3.         10.       E-DDC Compliance       3.         10.1       Older Designs       3.         10.2       New Display Designs       3.         10.3       New Host Subsystem Designs       3.         10.4       1°C Bus       3.         10.5       E-DDC Unique Features       3.         10.5.1       Segment Pointer       3.         10.5.2       Power Pin       4.         10.5.3       EDID / DisplayID Available with Display Powered Off       4.         10.6       Co-existence of E-DDC, DDC/CI and HDCP       4.         11       Appendix A: Answers to Commonly Asked Questions       4.                                                                                                                                                                                                 |     |                    | •                                                   |    |

| 7.4.2 DisplayPort External Connector Pin-Out       36         7.4.3 Power Requirements       36         8. DisplayPort and DDC/E-DDC       37         9. Enhanced DDC System/Display Combinations       36         9.1 Interoperability       31         9.1.1 DDC Host System Connected to an E-DDC Display       36         9.1.2 Enhanced DDC Host Connected to a DDC Display       36         10. E-DDC Compliance       39         10.1 Older Designs       30         10.2 New Display Designs       30         10.3 New Host Subsystem Designs       31         10.4 I <sup>2</sup> C Bus       31         10.5 E-DDC Unique Features       32         10.5.1 Segment Pointer       33         10.5.2 Power Pin       44         10.5.3 EDID / DisplayID Available with Display Powered Off       44         10.6 Co-existence of E-DDC, DDC/CI and HDCP       44         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                               | 7.  |                    | * *                                                 |    |

| 7.4.3 Power Requirements       36         8. DisplayPort and DDC/E-DDC       37         9. Enhanced DDC System/Display Combinations       33         9.1 Interoperability       36         9.1.1 DDC Host System Connected to an E-DDC Display       36         9.1.2 Enhanced DDC Host Connected to a DDC Display       36         10. E-DDC Compliance       31         10.1 Older Designs       33         10.2 New Display Designs       36         10.3 New Host Subsystem Designs       36         10.4 I <sup>2</sup> C Bus       36         10.5 E-DDC Unique Features       36         10.5.1 Segment Pointer       36         10.5.2 Power Pin       46         10.5.3 EDID / DisplayID Available with Display Powered Off       46         10.6 Co-existence of E-DDC, DDC/CI and HDCP       46         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                    |                                                     |    |

| 8. DisplayPort and DDC/E-DDC       3         9. Enhanced DDC System/Display Combinations       3         9.1 Interoperability       3         9.1.1 DDC Host System Connected to an E-DDC Display       3         9.1.2 Enhanced DDC Host Connected to a DDC Display       3         10. E-DDC Compliance       3         10.1 Older Designs       3         10.2 New Display Designs       3         10.3 New Host Subsystem Designs       3         10.4 I <sup>2</sup> C Bus       3         10.5 E-DDC Unique Features       3         10.5.1 Segment Pointer       3         10.5.2 Power Pin       4         10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/Cl and HDCP       4         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                    | * *                                                 |    |

| 9. Enhanced DDC System/Display Combinations       33         9.1 Interoperability       36         9.1.1 DDC Host System Connected to an E-DDC Display       36         9.1.2 Enhanced DDC Host Connected to a DDC Display       36         10. E-DDC Compliance       39         10.1 Older Designs       31         10.2 New Display Designs       31         10.3 New Host Subsystem Designs       31         10.4 I <sup>2</sup> C Bus       31         10.5 E-DDC Unique Features       31         10.5.1 Segment Pointer       31         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                    | •                                                   |    |

| 9.1 Interoperability       33         9.1.1 DDC Host System Connected to an E-DDC Display       36         9.1.2 Enhanced DDC Host Connected to a DDC Display       37         10. E-DDC Compliance       39         10.1 Older Designs       30         10.2 New Display Designs       30         10.3 New Host Subsystem Designs       30         10.4 I C Bus       30         10.5 E-DDC Unique Features       30         10.5.1 Segment Pointer       30         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.  | Displa             | yPort and DDC/E-DDC                                 | 37 |

| 9.1.1 DDC Host System Connected to an E-DDC Display       36         9.1.2 Enhanced DDC Host Connected to a DDC Display       36         10. E-DDC Compliance       39         10.1 Older Designs       39         10.2 New Display Designs       39         10.3 New Host Subsystem Designs       39         10.4 I 2C Bus       39         10.5 E-DDC Unique Features       39         10.5.1 Segment Pointer       30         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9.  | Enhand             | ced DDC System/Display Combinations                 | 38 |

| 9.1.1 DDC Host System Connected to an E-DDC Display       36         9.1.2 Enhanced DDC Host Connected to a DDC Display       36         10. E-DDC Compliance       39         10.1 Older Designs       39         10.2 New Display Designs       39         10.3 New Host Subsystem Designs       39         10.4 I 2C Bus       39         10.5 E-DDC Unique Features       39         10.5.1 Segment Pointer       30         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9.  | .1 In              | teroperability                                      | 38 |

| 9.1.2 Enhanced DDC Host Connected to a DDC Display       36         10. E-DDC Compliance       37         10.1 Older Designs       38         10.2 New Display Designs       39         10.3 New Host Subsystem Designs       39         10.4 I <sup>2</sup> C Bus       39         10.5 E-DDC Unique Features       39         10.5.1 Segment Pointer       30         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                    | *                                                   |    |

| 10. E-DDC Compliance       39         10.1 Older Designs       39         10.2 New Display Designs       39         10.3 New Host Subsystem Designs       39         10.4 I C Bus       39         10.5 E-DDC Unique Features       39         10.5 I Segment Pointer       39         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 9.1.2              |                                                     |    |

| 10.1 Older Designs       39         10.2 New Display Designs       39         10.3 New Host Subsystem Designs       39         10.4 I 2C Bus       39         10.5 E-DDC Unique Features       39         10.5.1 Segment Pointer       39         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10. | E-D                |                                                     |    |

| 10.2 New Display Designs       39         10.3 New Host Subsystem Designs       39         10.4 I 2C Bus       39         10.5 E-DDC Unique Features       39         10.5.1 Segment Pointer       39         10.5.2 Power Pin       40         10.5.3 EDID / DisplayID Available with Display Powered Off       40         10.6 Co-existence of E-DDC, DDC/CI and HDCP       40         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10  | 0.1 OI             | lder Designs                                        | 39 |

| 10.3       New Host Subsystem Designs       39         10.4       I 2C Bus       39         10.5       E-DDC Unique Features       39         10.5.1       Segment Pointer       30         10.5.2       Power Pin       40         10.5.3       EDID / DisplayID Available with Display Powered Off       40         10.6       Co-existence of E-DDC, DDC/CI and HDCP       40         11.       Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10  |                    | e                                                   |    |

| 10.5E-DDC Unique Features3910.5.1Segment Pointer3110.5.2Power Pin4010.5.3EDID / DisplayID Available with Display Powered Off4010.6Co-existence of E-DDC, DDC/CI and HDCP4011.Appendix A: Answers to Commonly Asked Questions4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10  |                    |                                                     |    |

| 10.5.1 Segment Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10  | $0.4 	ext{ I}^{2}$ | C Bus                                               | 39 |

| 10.5.2 Power Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10  | 0.5 E-             | DDC Unique Features                                 | 39 |

| 10.5.3 EDID / DisplayID Available with Display Powered Off       4         10.6 Co-existence of E-DDC, DDC/CI and HDCP       4         11. Appendix A: Answers to Commonly Asked Questions       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 10.5.1             | Segment Pointer                                     | 39 |

| 10.6 Co-existence of E-DDC, DDC/CI and HDCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 10.5.2             |                                                     |    |

| 11. Appendix A: Answers to Commonly Asked Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                    | EDID / DisplayID Available with Display Powered Off | 40 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10  | 0.6 Co             | p-existence of E-DDC, DDC/CI and HDCP               | 40 |

| 12. Appendix B: Main Contribution History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11. | App                | endix A: Answers to Commonly Asked Questions        | 41 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12. | App                | endix B: Main Contribution History                  | 43 |

# **Tables**

| Table 1-1: Main Contributors to Version 1, Revision 2                             | <i>6</i> |

|-----------------------------------------------------------------------------------|----------|

| Table 1-1: Reference Documents                                                    |          |

| Table 2-1: Summary of DDC Communication Modes                                     | 11       |

| Table 5-1: DDC and E-DDC Device Addresses - EDID                                  | 20       |

| Table 5-2: DDC and E-DDC Device Addresses - DisplayID                             | 20       |

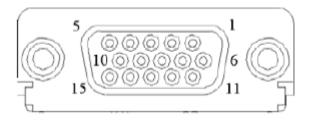

| Table 7-1: 15-pin D-type Connector Pinouts                                        |          |

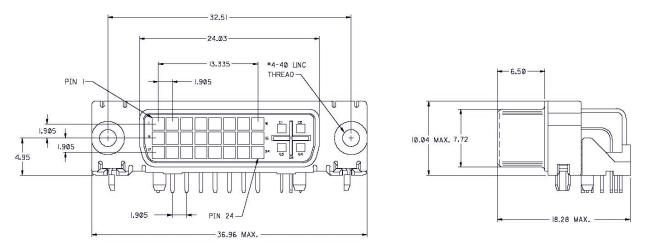

| Table 7-2: DVI Connector Pin-out                                                  |          |

| Table 7-3: HDMI-A & HDMI-B Connector Pin-outs                                     | 34       |

| Table 7-4: DisplayPort External Connector Pin-out                                 | 36       |

| Table 10-1: Segment pointer tests                                                 | 39       |

| Table 10-2: Power Pin Tests                                                       |          |

| Table 10-3: EDID and/or DisplayID Read with no Display Power                      | 40       |

| Table 11-1: Answers to Commonly Asked Questions about E-DDC and the VGA Interface |          |

| Table 12-1: Main Contributors to E-DDC Version 1.0                                |          |

| Table 12-2: Main Contributors to E-DDC Version 1.1                                | 43       |

| Figures                                                                           |          |

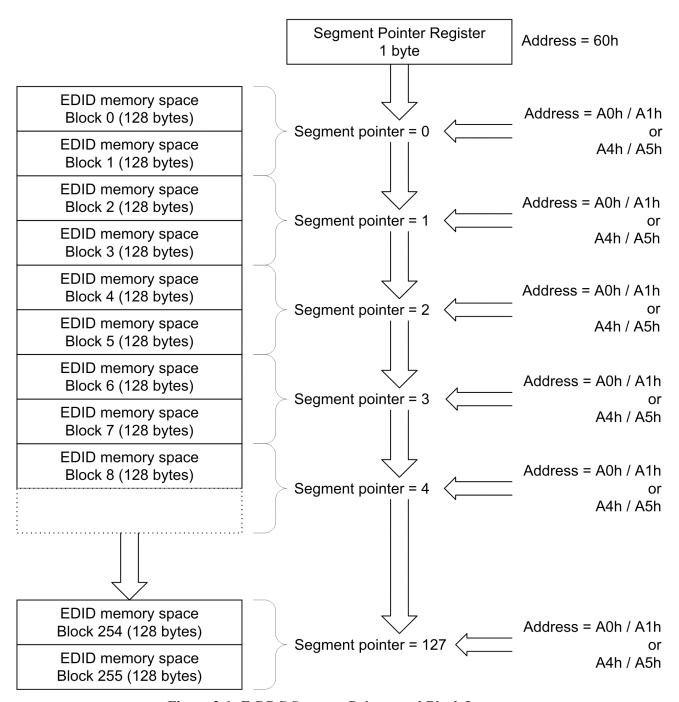

| Figure 2-1: E-DDC Segment Pointer and Block Layout                                | 15       |

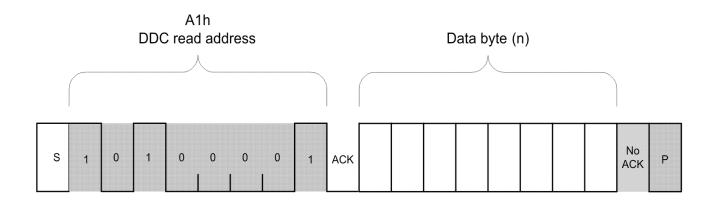

| Figure 6-1: DDC Read at the Current Address                                       | 23       |

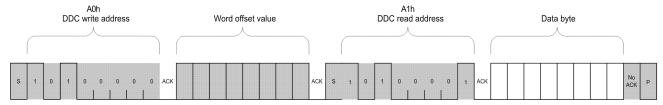

| Figure 6-2: DDC random read operation                                             | 24       |

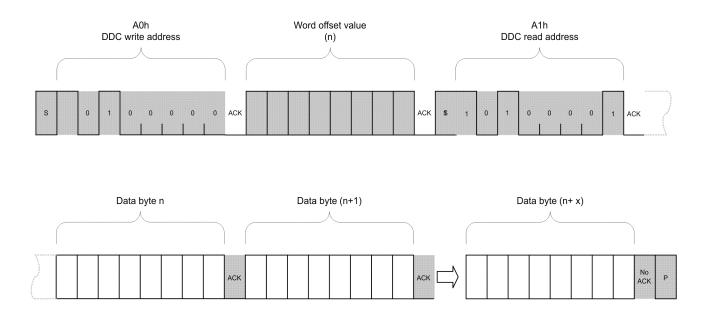

| Figure 6-3: DDC Sequential Read Operation                                         | 25       |

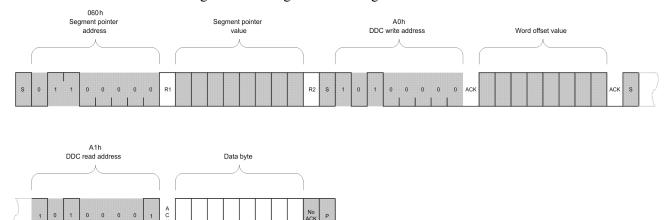

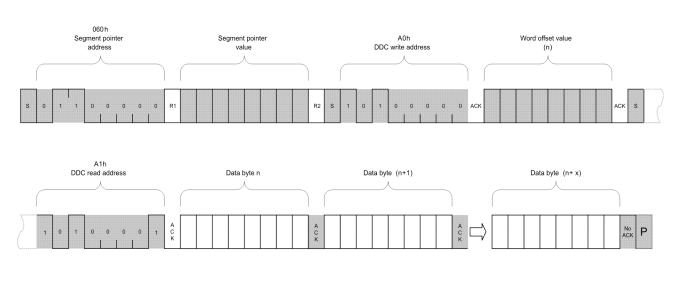

| Figure 6-4: E-DDC Random Read Operation                                           | 26       |

| Figure 6-5: DDC Sequential Read Operation                                         | 27       |

| Figure 7-1: VGA Socket                                                            | 28       |

| Figure 7-2: DVI -I Socket Drawing                                                 | 30       |

| Figure 7-3: DVI-D Socket Drawing                                                  | 30       |

| Figure 7-4: HDMI-A Connector                                                      | 32       |

| Figure 7-5: HDMI-B Connector                                                      | 33       |

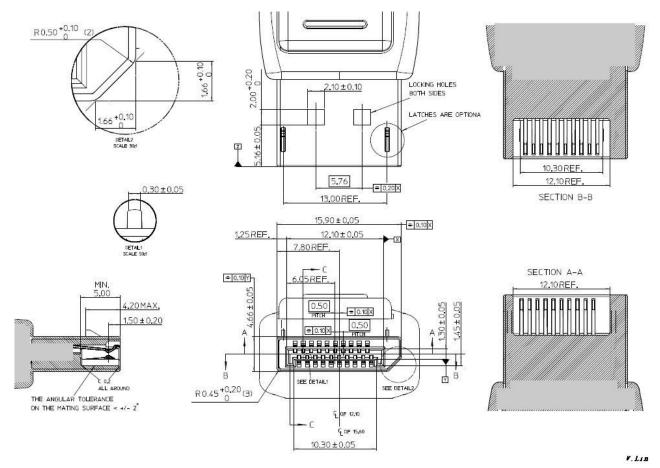

| Figure 7-6: DisplayPort External Connector Receptacle                             | 35       |

| Figure 7-7: DisplayPort External Connector Plug                                   | 36       |

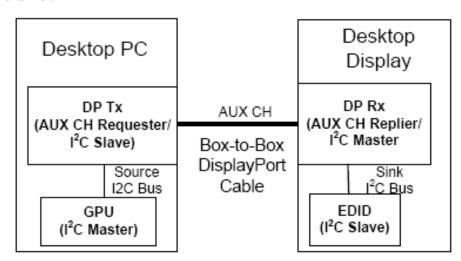

| Figure 8-1: DisplayPort Manning of I <sup>2</sup> C to AUX Channel                | 37       |

#### Preface

# **Intellectual Property**

Copyright © 1994 - 2007 Video Electronics Standards Association. All rights reserved.

While every precaution has been taken in the preparation of this standard, the Video Electronics Standards Association and its contributors assume no responsibility for errors or omissions, and make no warranties, expressed or implied, of functionality or suitability for any purpose.

#### **Trademarks**

All trademarks used within this document are the property of their respective owners. VESA, E-EDID, DCM, DDC/CI, DI-EXT, DisplayID, DisplayPort, MCCS, LS-EXT, PnP, and VBE/DDC are registered trademarks of the Video Electronics Standards Association.

I<sup>2</sup>C is a trademark of Philips.

DVI is a trademark of the Digital Display Working Group.

HDMI and High Definition Multimedia Interface are trademarks of HDMI Licensing, LLC.

HDCP (content protection standard) is from Digital Content Protection, LLC. (www.digital-cp.com)

#### **Patents**

VESA draws attention to the fact that it is claimed that compliance with this specification may involve the use of a patent or other intellectual property. VESA takes no position concerning the evidence, validity, and scope of this *IPR*.

Attention is drawn to the fact that some of the elements of this VESA *Specification* may be the subject of *IPR* other than that identified above. VESA shall not be responsible for identifying any or all such *IPR*, and has made no inquiry into the possible existence of any such *IPR*.

THIS SPECIFICATION IS BEING OFFERED WITHOUT ANY WARRANTY WHATSOEVER, AND IN PARTICULAR, ANY WARRANTY OF NON-INFRINGEMENT IS EXPRESSLY DISCLAIMED. ANY IMPLEMENTATION OF THIS SPECIFICATION SHALL BE MADE ENTIRELY AT THE IMPLEMENTER'S OWN RISK, AND NEITHER VESA, NOR ANY OF ITS MEMBERS OR SUBMITTERS, SHALL HAVE ANY LIABILITY WHATSOEVER TO ANY IMPLEMENTER OR THIRD PARTY FOR ANY DAMAGES OF ANY NATURE WHATSOEVER DIRECTLY OR INDIRECTLY ARISING FROM THE IMPLEMENTATION OF THIS SPECIFICATION.

### **Support**

Clarifications and application notes to support this standard may be written. To obtain the latest standard and any support documentation, contact VESA.

If you have a product that incorporates the Enhanced Display Data Channel (E-DDC), you should ask the company that manufactured your product for assistance. If you are a manufacturer, VESA can assist you with any clarification you may require. Submit all comments or reported errors in writing to VESA using one of the following methods.

• Fax: 510 651 5127, direct this fax to Technical Support at VESA

e-mail: support@vesa.orgMail: Technical Support

Video Electronics Standards Association

39899 Balentine Drive, Suite 125

Newark, CA 94560

# Acknowledgements

This document would not have been possible without the efforts of the VESA Display Systems Committee's EDDC Task Group. In particular, the following individuals and their companies contributed significant time and knowledge.

Table 1-1: Main Contributors to Version 1, Revision 2

| Name               | Company                |                       |

|--------------------|------------------------|-----------------------|

| Syed Athar Hussain | AMD                    |                       |

| Ashley Saldanha    | EnTech Taiwan          | Task Group Chair      |

| Ian Miller         | Ian Miller Consultancy | Document Editor       |

| Chandra Kondura    | Intel                  |                       |

| Matt Sottek        | Intel                  |                       |

| Christian Hofmann  | Kontron                |                       |

| Jim Webb           | Xponent                | Task Group Vice-chair |

| Alain d'Hautecourt | ViewSonic              |                       |

# Revision History

# Version 1 September 2, 1999

Initial release of the standard. The body of the standard is derived from the VESA DDC Version 3 Standard. The major changes were the addition of the E-DDC protocols, removal of DDC1 protocol and clarification to the DDC power requirements.

### Version 1, Revision 1 March 24, 2004

A revision and update to the E-DDC standard to encompass usage in consumer electronic products and video interfaces other than VGA, with text clarified in several places.

### Version 1, Revision 2 December 26, 2007

This revision updates the E-DDC standard, expanding its scope to encompass DisplayID and DisplayPort, and correcting and clarifying text in several places.

### 1. OVERVIEW

# 1.1 Summary

The Display Data Channel, DDC, is a subset of the I<sup>2</sup>C bus used to provide bi-directional communications between a host device and an attached display. In their basic form, the capabilities are limited to allowing the host to request and read the EDID or the DisplayID from the display – EDID and DisplayID are alternate structures that each contains information about the capabilities of the display.

In the DDC standard, the host could only access a very limited address space which constrained the size of the EDID or DisplayID. E-DDC is fully backward compatible with DDC, but enables a significantly larger address space to be used.

#### **Notes:**

- 1) The content and format of EDID are not defined in this standard; refer to the VESA Enhanced Extended Display Identification Data Standard (E-EDID) and, where appropriate, the various VESA E-EDID extension block standards and the CEA E-EDID extension defined in the CEA-861 standard.

- 2) The content and format of DisplayID are not defined in this standard. Refer to the VESA Display Identification (DisplayID) Standard.

The scope of this document is to provide a detailed description of the operation of E-DDC and its implementation.

However, in addition to serving to request and transmit EDID and DisplayID, the Display Data Channel also allows more advanced communication between the display and host. This enables the host to control many aspects of the display capabilities and functions. For details of this communication mode see the VESA Display Data Channel Command Interface Standard (DDC/CI) and for details of commands see the VESA Monitor Command and Control Set (MCCS) standard.

<u>Note:</u> The "monitor" in the MCCS name should not be taken to mean that it only applies to computer displays; many MCCS commands are applicable to any electronic display and some are exclusively for television purposes.

DDC communications has been widely implemented in a number of video interfaces including VGA (15 pin high-density D-sub), DVI and HDMI. Support is also provided in the VESA DisplayPort standard via emulation.

This document does not specify how the E-DDC interfaces communicate to the host CPU and GPU address and I/O spaces.

Earlier versions of the DDC and E-DDC standards introduced and supported a very simple unidirectional, display to host, DDC1 mode – this mode is no longer supported by VESA.

The VESA task group responsible for the development of this standard has spent considerable time considering how best to manage the situation where there are two (EDID and DisplayID) schemes that may be used to convey capability information from the display to the host. The conclusion can be summarized as follows:

- The data at I<sup>2</sup>C slave addresses A0h / A1h will be the primary location for display capability information.

- A second pair of I<sup>2</sup>C slave addresses at A4h / A5h will be the secondary location for display capability information.

Further details are contained in Section 3.

## 1.2 Background

Early personal computer monitor identification schemes were only capable of handling a limited number of display types and parameters. Since these schemes carried very little information about the capabilities of the display, they were of limited value.

Earlier versions of DDC and EDID defined a communication method and configuration data appropriate for traditional CRT displays, but were limited in their support of other display types and the amount of data that could be supported in the display. Over time, VESA introduced enhanced versions of the DDC and EDID standards, E-DDC and E-EDID respectively, with new capabilities.

As new display technologies have been introduced to the market, support for communication methods and configuration information suitable for these displays has become a necessity. In recent years displays intended for digital and high definition television have also adopted DDC communication to transfer EDID from the display to the host.

DisplayID is a new (2007) standard which has a number of advantages expected to coexist with EDID for some time. Some products may have either an EDID or a DisplayID, depending on the market. Others may implement both EDID and DisplayID within a single display.

DisplayID advantages:

- Modular

- o The manufacturer selects which blocks are appropriate for the product

- Flexible block size

- Many of the block definitions have variable lengths so that they can be used or either simple or advanced display capabilities

- Efficient

- o Block types and size are matched to the requirements of the individual display type.

- o Overall size is determined by the product requirements.

- No assumption about display technology

- o No implicit assumptions about the display technology being used.

<u>Note:</u> For convenience and compatibility with EDID structures, it is implied in this document that DisplayID is organized in 128 byte blocks. However, DisplayID actually has a variable length – see DisplayID standard for details. The techniques described here will work, but may not be the most efficient when applied to DisplayID.

# 1.3 Significant Changes in Current E-DDC Revision

This revision (1.2) updates the E-DDC standard with clarification and corrections together with support for DisplayID. Changes may be summarized as:

- No support for the DDC1 mode of operation

- Clarification of the use of DDC on multiple interfaces VGA, DVI, HDMI and DisplayPort

- Addition of a compliance section section 10

- Deletion of notes regarding possible move from +5V to +3.3V for DDC power

- Support for DisplayID added.

### 1.4 Reference Documents

Versions identified here are current but users of this standard are advised to ensure they have the latest versions of reference standards and documents.

**Table 1-1: Reference Documents**

| Document                                                                         | Version / Revision     | Date           |

|----------------------------------------------------------------------------------|------------------------|----------------|

| VESA Glossary of Terms – see www.vesa.org                                        | Current                | Current        |

| VESA Policy 200, Intellectual Property Rights                                    | В                      | December 2004  |

| VESA Video BIOS extensions for Display Data Channel (VBE/DDC)                    | Version 1 / Revision 1 | November 1999  |

| VESA Enhanced Extended Display Identification Data (E-EDID)                      | Version A / Revision 2 | September 2006 |

| VESA Monitor Command and Control Set (MCCS)                                      | Version 3              | July 2006      |

| VESA Display Data Channel – Command Interface (DDC/CI)                           | Version 1 / Revision 1 | October 2004   |

| VESA Plug & Play (PnP) Standard for the Display/Graphics Subsystem               | Release A              | June 2004      |

| VESA E-EDID Localized String Extension (LS-EXT <sup>™</sup> ) Standard           | Release A              | July 2003      |

| VESA Display Color Management (DCM <sup>™</sup> ) Standard                       | Version 1              | January 2003   |

| VESA Display Information Extension (DI-EXT <sup>™</sup> ) Block Standard         | Release A              | August 2001    |

| VESA Display Identification (DisplayID) Standard                                 | Version 1              | December 2007  |

| VESA DisplayPort Standard                                                        | Version 1 / Revision 1 | March 2007     |

| The I <sup>2</sup> C Bus Specification                                           | Version 2.1            | January 2001   |

| Microsoft Plug and Play for Windows 2000 and Windows XP                          | White Paper            | December 2001  |

| IBM Personal System/2 Hardware Interface Technical Reference - Common Interfaces | First Edition          | 1987           |

| CEA-861 Standard, A DTV Profile for Uncompressed High Speed Digital Interfaces   | D (or newer)           | 2006           |

| Digital Visual Interface (DVI)                                                   | Revision 1.0           | April 1999     |

| High-Definition Multimedia Interface (HDMI)                                      | Version 1.3            | June 2006      |

| High-bandwidth Digital Content Protection Scheme (HDCP)                          | Version 1.3            | December 2006  |

#### 2. DEFINITIONS

In the following sections and unless otherwise specified "EDID" refers to all revisions of EDID Version 1, up to and inclusive of the latest revision - see the latest VESA E-EDID standard for details.

#### 2.1 Data formats

#### 2.1.1 Enhanced Extended Display Identification Data: E-EDID

The E-EDID standard defines a 128 byte EDID structure containing the display identity and the basic display specifications. It also defines support for a number of 128 byte extensions which allow additional information to be communicated.